The devil is in the fine print.

From the Web

魔鬼总是在文件细则中。

网络格言

# 3.1 RISC-V的历史

RISC-V 最早源自 2010 年夏天美国加州大学伯克利分校 Krste Asanović 教授主持的一个关于开源计算机系统的研究项目。该项目得到了美国国防高级研究计划局(Defense Advanced Research Projects Agency, DARPA)的资助,后来成为RISC-V的前身[这里顺便提一句,国际互联网Internet的前身ARPANET(Advanced Research Projects Agency Network,高级研究计划局网络)也是由 DARPA 资助的]。

RISC-V中的字母 V表示第五代的意思,所以发音时应该发作"RISC-Five",表示它师承于伯克利分校之前开发的一系列 RISC 指令集。根据 RISC-V 的族谱,RISC-V之前四代指令集都产生于 20 世纪 80 年代。当然,RISC-V 在其形成过程中,也从其他各种流行的指令集(MIPS、SPARC、ARM等)中吸取了经验教训。

在 RISC-V 问世之际,移动计算主要由 ARM 处理器把持,而 Intel 公司的 x86 处理器则占据了大部分的桌面计算市场,RISC-V 的出现给这两大巨头带来了挑战。与这两大巨头的指令集不同的是,RISC-V 是一个自由和开放的指令集,它的标准化工作由 RISC-V 基金会主持,该组织目前有超过 100 个会员,并在不断扩大之中。对任何想要用 RISC-V 设计实现处理器的公司与个人,他们都不会受到来自 RISC-V 基金会的限制,也无须向 RISC-V 基金会支付授权费用。基金会各会员公司也承诺不会就 RISC-V 的基本议题向其他成员发起诉讼。

由于 RISC-V 没有上面提到的这些限制,因此很快得到了开源社区的大力拥护。 面对 RISC-V 的攻城略地,ARM 也开始予以反击。2018 年夏,ARM 上线了一个 名为 riscv-basics.com 的网站,对 RISC-V 发起舆论战。但是这种做法很快受到了来自各方的诟病,甚至连 ARM 自己的员工都对此做法表示不满。迫于各方压力,ARM 很快就关闭了该网站。

另外,为了促进 RISC-V 的产业化,RISC-V 的主要开发成员还于 2015 年成立

了一家叫 SiFive 的初创公司,向市场提供各类 RISC-V 的处理器内核,以及相关的软件工具和开发套件。

## 3.2

## 8051的CISC指令集与RISC-V的比较

#### 3.2.1 8051 指令集简介

提到 RISC(Reduced Instruction Set Computer,精简指令集计算机),就必然也会提到 CISC(Complex Instruction Set Computer,复杂指令集计算机)。在许多嵌入式系统中得到广泛使用的 8051 单片机,便是 CISC 指令集的典型代表。笔者在开始设计 RISC-V 处理器之前,也曾做过一款 1T(单时钟周期)8051 处理器的设计,所以对这两类不同类型的指令集都有深入了解。这里笔者愿意将这些体会做个总结,并由此来反映 RISC-V 在技术设计上的优势。

可能有许多读者对 8051 单片机早已熟悉,该单片机是由美国 Intel 公司于 20 世纪 80 年代推出的一款 8 位单片机。由于该单片机方便易用,许多公司都推出了第三方的兼容设计。直到今天,8051 单片机依然被许多嵌入式系统所选用。

然而在 20 世纪 80 年代该单片机刚刚问世时,半导体的制造工艺还只能达到 µm 级,处理器所能达到的时钟频率偏低。而且当时硬件设计语言还处于起步阶段,也缺乏自动设计的工具,软件多以手工汇编编程为主。这就导致流水线设计的优势无法得到发挥,并且每条指令需要多个时钟周期才能完成。由于上述原因,当时的指令集设计往往具有以下特点:

- (1) 尽量在每条指令中实现更多的功能。例如 8051 的 CJNE 指令,就需要在一条指令中依次实现:

- ① 与累加器做减法。

- ② 修改进位标示。

- ③ 将结果做相等比较。

71

- ④ 根据比较结果决定是否跳转。

- (2)指令集庞大,以实现更多的复杂功能。例如8051虽然是8位单片机, 其指令集却包含高达255种不同的指令和格式。

- (3)由于以上两点,导致变长指令的出现,以提高内存利用率。8051的 指令就有单字节、双字节与三字节三种不同的种类,而且除了对指令解码以外, 没有其他的手段帮助判定指令长度。

- (4)寻址方式众多。例如在8051指令集中,对数值的操作包括如下方式:

- ①立即数寻址。将常数包含在指令中。

- ② 直接寻址。将内存地址包含在指令中。

- ③ 间接寻址。将内存地址放入寄存器中,然后将寄存器地址包含在指令中。

- ④ 寄存器寻址。将操作数放入寄存器中,然后将寄存器地址包含在指令中。

由于众多的寻址方式,同一个功能在指令集中就可能对应多种指令格式。例如 在 8051 指令集中, 光是一个加法指令就有 12 种不同格式。类似地, 跳转指令也存 在多种的寻址方式和指令格式。

8051 指令集的特点,很大程度上也代表了当时众多 CISC 指令集的共同特点。这种特点是与当时半导体制造水平和软件发展水平相匹配的。随着半导体加工工艺的不断进步和软件开发水平的提高,流水线和高时钟频率的设计开始在处理器设计中流行,汇编语言也开始被 C/C++ 这类高级编程语言所替代。尽管 8051 是一个非常长寿的指令集,自问世近 40 年,依然被业界广泛采用,但是今天市面上出现的8051 处理器,却早已和它们的祖先大不一样了。

8051 的第一代产品,其时钟频率只有 12 MHz,每个指令需要 12 个时钟周期才能完成。而今天我们所使用的 8051 处理器,都是增强型处理器,除了有更丰富的外围设备外,其增强之处主要表现在:

#### (1) 时钟频率大幅提高。

- (2)指令的吞吐率大幅提高,对大部分的指令,都可以做到在单个时钟周期内完成即我们通常说的1T8051。

- (3) 在软件上,支持 C语言的开发环境。

换句话说,今天的增强型 8051 处理器,虽然其指令集还是 40 年前的那个指令集,但是其内部实现却早已经在原型基础上进行了 RISC 改造(实际上,类似的 RISC 改造也同样发生在 Intel 的 x86 处理器上)。

<u>说明</u>:由于指令集设计的缺陷,这种对 CISC 指令集的 RISC 实现不可避免 地要在硬件上付出一定的代价。下面就以笔者主持设计的 PulseRain FP51-1T MCU 为例,对此具体加以说明。

## 3.2.2 8051 指令集对处理器设计的负面影响

PulseRain FP51-1T MCU 是美国 PulseRain Technology 公司推出的一款针对 FPGA 的 8 位微控制器,其内部的处理器内核是一个增强型 8051,可以对大部分的 8051 指令实现 1T 吞吐率,并且在 FPGA 上可以实现很高的时钟频率(在 Intel MAX10 C8 级器件上主频可以达到 100 MHz)。

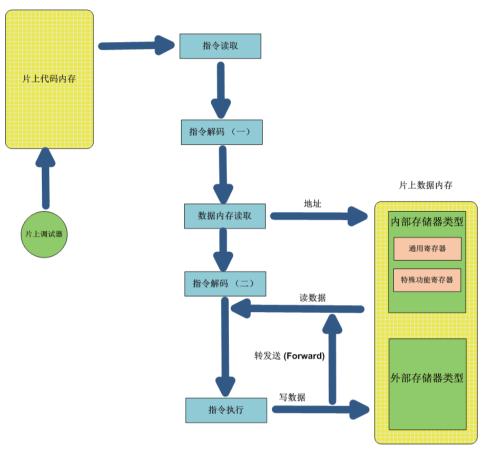

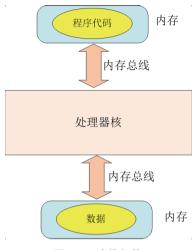

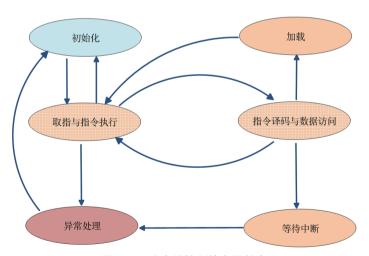

8051 的流水线实现如图 3-1 所示,该处理器的内部有一个 5 级流水线,包含指令读取、指令解码(一)、数据内存读取、指令解码(二)和指令执行。尽管该处理器在 FPGA 上有优秀的性能表现,然而由于 8051 指令集本身的缺陷,使得设计者不得不以额外的逻辑资源为代价来换取更高的性能。最后的结果就是与同样时钟频率的 RISC-V 处理器相比,8 位 8051 内核居然比 32 位 RISC-V 内核消耗更多的逻辑资源,占用更大的芯片面积,而更大的芯片面积意味着更加耗电。对 FPGA器件来说,这些还不是一个太大的问题,但是对专用芯片(ASIC),特别是移动设备的专用芯片来说,更多的耗电往往意味着更短的电池寿命(Battery Life),这可能也是 Intel x86 处理器始终无法在移动设备市场上打开局面的原因之一。

图3-1 8051 的流水线实现

具体来说,8051 指令集的特点会对处理器的RISC 实现产生如下负面影响:

#### 1)尽量在每条指令中实现更多的功能

为了在实现这些复杂功能的同时保持高吞吐率,流水线的设计者不得不花更多的时间规划流水线的各级。即便如此,有些指令依然无法实现单周期吞吐,例如上文提到的 CJNE 指令,就需要两个时钟周期。

另外,现代的8051处理器开发,早已经采用C语言代替了早期的汇编语言。 而高级语言的编译器往往很难把这类复杂、多功能机器指令的威力全部发挥出来, 有违当初指令集的设计初衷。

当然,指令集复杂这个特点也并非一无是处。由于 CISC 指令集的指令复杂,

也使得其代码密度(Code Density)一般要优于同等字宽的 RISC 处理器。

#### 2) 庞大的指令集

庞大的指令集必然导致指令的解码阶段变得更为复杂,需要耗费更多的逻辑资源。读者可能已经注意到,在图 3-1 所示的 5 级流水线中,指令集被分为两部分,对它们各自的解码分别占用了流水线的一级。这样设计的原因之一就是为了在庞大指令集下实现高吞吐率、高时钟频率,而不得不做出的妥协。同样时钟频率的RISC-V 处理器,由于指令集比较精简,就无需做这样的妥协,从而大大节省了逻辑资源,简化了流水线设计。

#### 3)由于以上两点,导致变长指令的出现,以提高内存利用率

8051 的指令有单字节、双字节和三字节三种不同的种类,除解码(Decode)外,没有其他的手段帮助判定指令长度。这种变长的指令结构,导致指令之间的边界很难判定,甚至有可能导致内存的非对齐读取(Unaligned Memory Access),从而对流水线的取指器(Instruction Fetch)设计带来挑战。

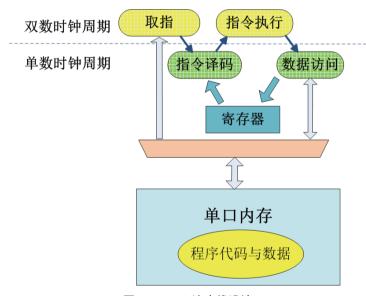

幸运的是,8051的内存架构是哈佛架构,其代码与数据在不同的地址空间中分开存放。这就使得代码存储部分可以单独做一些优化设计。在图 3-1 中左边部分的片上代码内存,实际上被分成 4 个 8 位宽的存储体,这样对代码内存的一次读取就可以得到 4 字节,从而保证至少可以有一条完整的指令。然而即便如此,由于8051指令集没有其他辅助手段来帮助判定指令长度,为了确定指令的边界,8051的取指器不得不为此花费比 RISC-V 更多的逻辑资源。

#### 4) 众多的寻址方式

由于 8051 存在众多的寻址方式,使得指令集中的许多指令都可以访问内存。这导致流水线的数据冲突(Data Hazard)很难判断,有时不得不通过硬件自动插入空操作(Null Operation, NOP)来保持数据的正确和完整。这样既消耗了逻辑资源,又降低了流水线的效率,从而对功耗和性能造成双重打击。

<u>说明</u>:虽然 8051 指令集有其历史局限性,但是 8051 处理器却由于其短小精悍、性价比高,一直为笔者所钟爱。其虽历四十载,依然廉颇未老,不乏拥趸。

#### 3.2.3 RISC-V 指令集对处理器设计的正面影响

8051 指令集的缺陷, 在 RISC-V 中都得到了避免, 具体说明如下。

#### 1. 引入指令长度编码

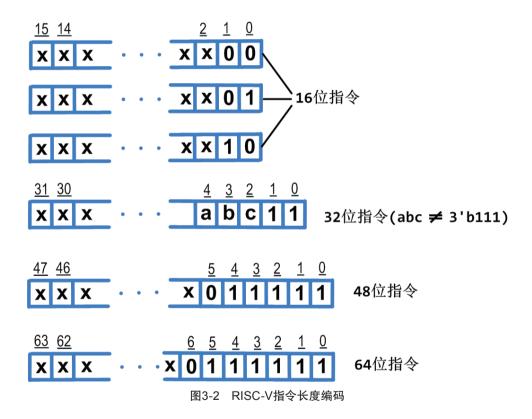

8051 指令集除了对指令解码以外,没有其他的辅助手段帮助判定指令长度,而 RISC-V 则可以通过指令的低位部分来判断指令的长度,被称为指令长度编码 (Instruction Length Encoding)。图 3-2 展示了 16~64 位指令的编码方式。64 位以上的编码方式,可以在 RISC-V 官方标准中找到。

指令长度编码的引入,大大简化了流水线取指器的设计,在取指时,硬件只需要集中优化边界对齐的内存读取就可以了。而对非对齐的访问,则可以通过产生异常,让软件处理器来处理。这样既节省了逻辑资源,又不影响处理器的性能。

#### 2. 指令集规模较小, 指令格式规整

尽管不是 8 位指令集, RISC-V 的指令集规模却比 8051 这样的 8 位指令集要小许多。RISC-V 的 32 位基础整数指令集只有 47 条指令,即使算上 8 条乘除法扩展指令,其指令总数也不到 8051 指令集规模的 1/4。指令集的小巧使得指令的解码器变得简单,更无须像图 3-1 中那样将指令集分成两部分来分别解码。

同时,RISC-V 的指令格式也非常规整,除了指令长度编码总是处在指令低位以外,在不同指令格式之间,操作码、源寄存器和目标寄存器总是位于相同的位置上。例如在RISC-V 32 位基础整数指令集中(RV32I),操作码总是占用低7位,而源寄存器1和2(rs1,rs2)则分别占据15~19位与20~24位。目标寄存器(rd)则占用7~11位(位索引以0为参考起点)。这种规整的指令格式进一步简化了指令解码器和指令执行器的设计。

#### 3. 每条指令实现单个功能

与 CISC 指令集的设计思想截然相反, RISC-V 指令集中的每条指令只集中于优化实现单个的功能,这种将复杂任务通过多个单功能的指令来实现的做法也一直是 RISC 指令集的指导思想。因为这样可以简化流水线的设计,从而能实现更高的时钟主频,最终可以让 RISC 获得比 CISC 更佳的总体性能。

#### 4. 内存访问只能通过 LOAD/STORE

与8051 指令集中,具有众多的寻址方式不同,在RISC-V 指令集中,对内存的读写只能通过 LOAD 指令和 STORE 指令实现。而其他的指令,都只能以寄存器为操作对象。没有了复杂的内存寻址方式,使得流水线对数据冲突(Data Hazard)可以及早做出正确的判断,并通过流水线各级之间的转送加以处理,而不需要插入空操作(NOP),极大提高了代码的执行效率。当然,这一特点也是RISC 指令集的共有特点之一。

至此我们可以看到, CISC 指令集的那些历史局限性, 在 RISC-V 指令集中都得到了突破。下面的章节会将 RISC-V 与其他的主流 RISC 指令集做对比, 并展示其设计上的考量与取舍。

## 3.3 RISC-V与其他RISC指令集的比较

根据 Andrew Waterman 的博士论文(Andrew Waterman 是 RISC-V 创始人之一, Krste Asanović 教授的学生), RISC-V 在当初的设计目标中和嵌入式处理器相关的部分如下:

- (1)指令集规模小,要求模块化并可扩展。

- (2)指令集设计独立于具体的处理器实现。

- (3) 支持 16 位与 32 位混合编程,以提高代码密度。

- (4)对 C/C++等编程语言提供硬件支持。

- (5)将用户指令集(User-Level ISA)和特权架构(Privileged Architecture)做正交分割(Orthogonalize),即不同特权架构的处理器可以在应用二进制接口(Application Binary Interface, ABI)层面做到代码互相兼容。

基于以上的设计目标,RISC-V对其他主流指令集的利弊都做了一番深入的研究,并做出了以下改进:

(1)将指令集分为基础指令集与扩展指令集。在处理器实现时,基础指令集是强制要求的,但扩展部分可选。

这样的安排在设计之初就为未来的历史演进留下了余地,避免了其他的指令级随着历史演进而愈来愈臃肿的问题(例如 ARM 指令集,在 ARMv7 中仅整数指令集部分就包含高达 600 条指令)。

(2) 去除了对跳转指令延迟槽的支持。

延迟槽(Delay Slot)在许多通用的 RISC 指令集(如 MIPS 和 SPARC)中都包含,甚至在专用数字信号处理器(例如 TI 的 C5x DSP)上也有支持。

## 第 3 章 RISC-V 指令集

延迟槽的目的是提高流水线的利用率,当跳转发生时,硬件不得不清空流水线,重新设置指令取指器。而这时,如果那些紧随在跳转指令之后进入流水线的指令(即延迟槽中的指令)可以继续被完全执行,而不被丢弃,则跳转指令的开销就可以被降低。

延迟槽实际上是把一部分工作量转移给了软件,而且严重限制了处理器的实现方式,所以 RISC-V 对此做了舍弃。不过,RISC-V 的设计者将比较和 跳转做了紧密的结合,对跳转指令的效率问题给出了另外一种解决方案。

## (3)取消对寄存器窗口的支持。

在函数调用时,编译器往往会插入开场白(Prologue)和收场白(Epilogue)代码来传递参数,并保存寄存器到栈上。当函数嵌套层次比较深时,这种开场白和收场白代码的开销就显得很可观。为了降低函数调用中的这部分开销,在加州大学伯克利分校设计的第一代 RISC 处理器和后来 SUN 公司的 SPARC 处理器当中,都引入了寄存器窗口的设计,也就是在处理器中包含了多套通用寄存器。当函数调用发生时,主调函数(Caller)和被调函数(Callee)共享现有的这套通用寄存器,同时硬件还会给被调函数分配一套新的通用寄存器。这样在函数嵌套调用时,每次调用都无须再保存寄存器到栈上,从而大大降低了开场白和收场白的代码开销。

说明:这种设计的结果就是硬件开销变得很大,而且实际使用起来的效果并不理想,特别是当通用寄存器被耗尽时,其处理会变得非常麻烦和缓慢。因此 RISC-V 对此弃之不用,而代以类似 IBM S/390 中的毫码程序 (Millicode Routine)的办法。

#### (4) 支持 16 位指令扩展, 并支持 16 位与 32 位混合编程。

与 ARM 等其他指令集不同的是, RISC-V 的 16 位指令只是一个扩展, 并不是一个单独的指令集。而且每条 16 位指令都可以翻译成一条对应的 32 位指令, 从而简化了指令解码器的设计。

## 3.4 RISC-V基础指令集 (RV32I与RV32E)

RISC-V 的官方标准主要分成两部分:用户指令集(User-Level Instruction Set Architecture)与特权架构(Privileged Architecture)。

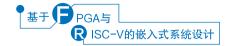

RISC-V 用户指令分类如图 3-3 所示,RISC-V 的用户指令集分为基础整数指令集(Base Integer Instruction Set)和扩展指令集(Extension)。根据处理器字长的不同,基础整数指令集又有 32 位、64 位和 128 位之分。而扩展指令集则有 16 位压缩指令(C,Compressed Instructions)、硬件乘除法(M,Integer Multiplication and Division)、取指隔离(Zifencei,Instruction Fetch Fence)等多种不同的扩展。考虑本书的主题主要是针对嵌入式系统开发,所以对 64 位和 128 位的指令将不予讨论。在本章节会主要讨论 RISC-V 32 位整数指令集(RV32I)和 32 位嵌入式指令。

## 3.4.1 RV32I与RV32E基础指令集简介

在 RISC-V 标准刚刚推出时,32 位的基础指令集只有 RV32I,即 32 位整数指令集。后来考虑嵌入式系统资源稀缺的情况,又制定了 RV32E 基础指令集,这里的字母 E 即代表嵌入式(Embedded)。RV32I 和 RV32E 的主要区别是在通用寄存器的数量上,在 RV32I 中,总共有32个32 位宽的通用寄存器,而 RV32E 只支持16个32 位宽的通用寄存器。另外 RV32E 仅支持 M、A、C 三种指令扩展。

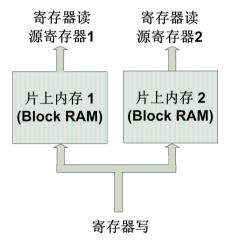

上述 RV32I 与 RV32E 的区别对 ASIC 的设计实现是有着实际意义的,在 ASIC 实现中,寄存器通常是通过触发器来实现的。对于面积优化的 RV32I 设计,移除 16 个通用寄存器大约可以节省 25% 的芯片面积; 而对于 FPGA 实现来说,移除 这 16 个寄存器并不能带来资源上面的节省。因为在 FPGA 当中,通用寄存器可以使用片上内存(Block Memory,BRAM)来实现。以 Intel MAX10 FPGA 为例,其 BRAM 是 M9K 类型,即每片 9Kb。而将 32 个 32 位通用寄存器用内存实现,只需要 1 024 位,会占用一片完整的 M9K BRAM。即使减少通用寄存器数量,其占用的 M9K 数量却依然还是一片,不会减少。基于这一点,本书将重点讨论 RV32I。

#### 3.4.2 RISC-V 地址空间

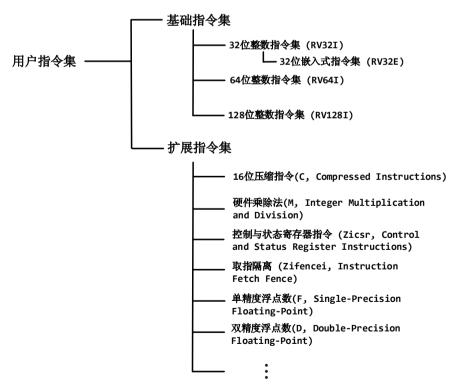

RISC-V 的地址空间如图 3-4 所示。RISC-V 总共有 3 个独立的地址空间。

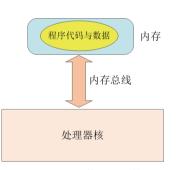

#### 1. 内存地址空间

内存地址空间可以用来分配给代码、数据,或者作为寄存器的内存映射(Memory Mapped Registers)。在物理实现时,代码和数据可以共用存储(von Neumann, 冯•诺依曼架构),也可以分别存储(Harvard,哈佛架构)。和其他的处理器一样,RISC-V的处理器也是通过程序计数器(Program Counter, PC)来指示当前正在执行的指令地址的。

在寄存器的内存映射部分,大部分的外围设备寄存器都会被映射到这个空间, 其中也包括机器模式的定时器(Mtime)和定时器触发值(Mtimecmp)。

#### 2. 通用寄存器

RV32I 指令集包含 32 个通用寄存器, 而 RV32E 只有 16 个这样的寄存器。

## 3. 控制与状态寄存器

在 RISC-V 的特权架构部分还对控制与状态寄存器(Control Status Register, CSR)做了定义,并单独分配了 12 位的地址空间。在用户指令集中,则专门定义了 Ziesr 指令集扩展来对 CSR 进行操作。

## 3.4.3 RV32I 通用寄存器与函数调用约定

RV32I 基础指令集总共定义了 32 个 32 位的通用寄存器。它们分别被标记为  $x0 \sim x31$ 。其中零号寄存器 x0 是只读寄存器,其值永远为零。

RISC-V 的设计目标之一就是对 C/C++ 等高级语言提供硬件支持,并保持不同处理器之间在 ABI 层面的相互兼容。RISC-V 的用户指令标准还对函数调用约定(Calling Convention)做了标准化,也就是对函数调用时,哪些寄存器需要保存,还对寄存器具体的职能分配做了规定(因为 RV32E 只有 16 个通用寄存器,所以

82

RV32E 的 ABI 和 RV32I 的 ABI 不兼容)。在用汇编语言编写时,这 32 个寄存器 的名称也根据其在调用约定中的职能而被重新命名。具体如表 3-1 所示。

| 寄存器名称   | 汇编名称                                  | <br>  功能描述      | 调用返回后其值  |

|---------|---------------------------------------|-----------------|----------|

| 可任命有你   | / / / / / / / / / / / / / / / / / / / | 初的细体            | 是否会保证不变  |

| x0      | zero                                  | 零寄存器            | 未定义      |

| x1      | ra                                    | 返回地址            | 否        |

| x2      | sp                                    | 栈指针             | 是        |

| x3      | gp                                    | 全局指针            | 未定义      |

| x4      | tp                                    | 线程指针            | 未定义      |

| VE      | tO.                                   | 临时寄存器,或者用作替代链接寄 | <u> </u> |

| x5      | lÜ                                    | 存器 ( 见后续章节详述 )  | 否        |

| x6      | t1                                    | 临时寄存器           | 否        |

| ×7      | t2                                    | 临时寄存器           | 否        |

| x8      | oO/fp                                 | 该寄存器需要被调函数予以保存, | 是        |

| ХО      | s0/fp                                 | 或也可用作调用栈的帧指针    | 走        |

| x9      | s1                                    | 该寄存器需要被调函数予以保存  | 是        |

| x10~x11 | a0~ a1                                | 函数参数或返回值        | 否        |

| x12~x17 | a2~a7                                 | 函数参数            | 否        |

| x18~x27 | s2~s11                                | 该寄存器需要被调函数予以保存  | 是        |

| x28~x31 | t3~t6                                 | 临时寄存器           | 否        |

表 3-1 函数调用约定的寄存器分配

<u>注意</u>: 需要指出的是,除了硬件指令集会对函数调用约定产生影响外,高级语言的编译器也会对其有影响。

例如,对下面的函数:

void dummy(int a, int b, int c, int d, int e);

不同的编译器可能对函数参数压栈的顺序有不一致的理解。有的会从左到右,以 a、b、c、d、e 的顺序压栈;有的则反之,从右到左压栈。这种编译器在函数调用约定上的不一致在 C 和 C++ 语言混合编程时经常发生。当 C++ 模块直接调用 C 语言模块时,链接器会给出警告或报错。通常的做法是在调用时,把 C 语言的 函数用 C++ 关键字 extern "C" 加以修饰说明,从而给编译器以明确的指示。

#### 3.4.4 RV32I 指令格式

RV32I 基本指令格式如图 3-5 所示, RV32I 的基本指令格式只有 4 种, 分别是寄存器类型(R-TYPE)、短立即数类型(I-TYPE)、内存存储类型(S-TYPE)、高位立即数类型(U-TYPE)。

| <u>31</u> | <u>25</u> | <u>24</u> | <u>20</u> |           | <u>15</u> | <u>14</u> |    | <u>12</u> | <u>11</u> | <u>7</u> <u>6</u> |     | 0        | R-TYPE            |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----|-----------|-----------|-------------------|-----|----------|-------------------|

|           | 功能        | 源寄        | 存器2       | 源寄        | 存器1       |           | 功能 |           | 目标寄存      | 字器                | 操作码 |          | 寄存器类型             |

| <u>31</u> |           |           | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |    | <u>12</u> | <u>11</u> | <u>7</u> <u>6</u> |     | <u>0</u> | T TVDE            |

|           | 立即数[      | 11:0]     |           | 源寄        | 存器1       |           | 功能 |           | 目标寄石      | 字器                | 操作码 |          | I-TYPE<br>短立即数类型  |

| <u>31</u> | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |    | <u>12</u> | <u>11</u> | <u>7 6</u>        |     | 0        |                   |

| 立即        | 数[11:5]   | 源寄        | 存器2       | 源寄        | 存器1       |           | 功能 |           | 立即数[4     | 4:0]              | 操作码 |          | S-TYPE<br>内存存储类型  |

| <u>31</u> |           |           |           |           |           |           |    | <u>12</u> | <u>11</u> | <u>7</u> <u>6</u> |     | <u>0</u> |                   |

|           |           | 立即        | 即数[3:     | 1:12]     |           |           |    |           | 目标寄存      | 字器                | 操作码 |          | U-TYPE<br>高位立即数类型 |

图3-5 RV32I基本指令格式

为了方便跳转指令,RV32I 还包含两种衍生格式 B-TYPE(Branch,条件跳转)与 J-TYPE(Jump,无条件跳转)。B-TYPE 衍生于 S-TYPE,B-TYPE 除了立即数的位排列与 S-TYPE 不一样外,其他的格式都与 S-TYPE 一样。J-TYPE 也是通过类似的方式衍生于 U-TYPE。用这种方式衍生新格式的目的是便于硬件产生目标地址。

上面这些格式,除 R-TYPE 外,其他的格式都需要把最高位(第 31 位)做符号扩展,以产生一个 32 位的立即数,作为指令的操作数。

图 3-5 所示的这些指令格式非常规整,其操作码、源寄存器和目标寄存器总是位于相同的位置上,简化了指令解码器的设计。

## 3.4.5 RV32I 算术与逻辑指令

#### 1. 立即数指令

1) 立即数加法

RV32I 立即数加法的定义如图 3-6 所示。这里特别要指出的是,和许多其他的

## 第3章 RISC-V 指令集

指令集不同,在 RV32I 当中并没有专门的状态寄存器和标记位来记录加法溢出。 对加法溢出的判断是通过在加法指令之后安排比较和跳转指令来实现的。对符号数 加法来说,只有正数加正数,或者负数加负数的情况才有可能发生溢出,所以溢出 可以通过符号位(与零比较)来判断。而对无符号数来说,其和应该不小于被加数, 所以溢出也可据此判断。

从 RV32I 对溢出标记的舍弃,也可以看出 RISC-V 非常强调指令集的简洁,极力减少不必要的硬件或指令,秉承了 RISC 指令集将复杂操作通过多条简单指令来实现的原始设计理念,可以说是不忘初心(这里实际上涉及一个更加复杂的话题,即 RISC-V 在设计时对条件编码(Condition Code)的舍弃)。具体的细节会在后续章节加以讨论。

从 ADDI 指令也可以衍生出空操作指令(NOP)。对 RISC-V 指令集,编译器一般会把 ADDI 中的立即数、源寄存器、目标寄存器都置为零,当作空操作指令使用。

## 2) 立即数比较

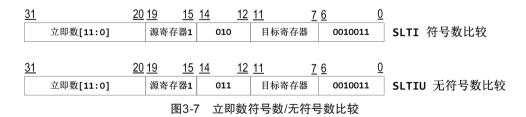

RV32I的立即数比较指令如图 3-7 所示。无论是符号数比较还是无符号数比较,图 3-7 中的 12 位立即数都应该通过符号位扩展变为 32 位立即数,然后根据指令 12 ~ 14 位中的功能定义,来决定比较方式符号数(SLTI)/无符号数(SLTIU)。

比较时,如果源寄存器中的值小于该 32 位立即数,则将目标寄存器置为 1; 否则置为零。由此,还可以通过 SLTIU 产生一个衍生指令:

SEQZ rd, rs  $\Leftrightarrow$  SLTIU rd, rs1, 1

该 SEQZ 指令可以很方便地根据源寄存器中的值产生零位标志,而无须添加额外的硬件或指令。

#### 3) 立即数逻辑操作

RV32I的立即数逻辑操作如图 3-8 所示。细心的读者可能已经注意到了, RV32I中并没有定义逻辑反操作(NOT)。实际上,逻辑反操作可以通过 XORI来 实现(只需将 XORI 指令中的立即数置为全 1 即可)。

| <u>31</u> |           | <u>20</u> | <u>19</u> <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> <u>7</u> | <u>6</u> |         | <u>0</u> |              |

|-----------|-----------|-----------|---------------------|-----------|-----|-----------|--------------------|----------|---------|----------|--------------|

|           | 立即数[11:0] |           | 源寄存器1               |           | 111 |           | 目标寄存器              |          | 0010011 |          | ANDI 立即数逻辑与  |

|           |           |           |                     |           |     |           |                    |          |         |          |              |

| <u>31</u> |           | <u>20</u> | <u>19</u> <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> <u>7</u> | <u>6</u> |         | 0        |              |

|           | 立即数[11:0] |           | 源寄存器1               |           | 110 |           | 目标寄存器              |          | 0010011 |          | ORI 立即数逻辑或   |

|           |           |           |                     |           |     |           |                    |          |         |          |              |

| <u>31</u> |           | <u>20</u> | <u>19</u> <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> <u>7</u> | <u>6</u> |         | 0        |              |

|           | 立即数[11:0] |           | 源寄存器1               |           | 100 |           | 目标寄存器              |          | 0010011 |          | XORI 立即数逻辑异或 |

|           |           |           |                     | 冬         | 3-8 | -         | 立即数逻辑操             | 11       |         |          |              |

## 4) 立即数移位操作

RV32I的立即数移位操作如图 3-9 所示。对逻辑左移操作,需要在最低有效位(Last Significant Bit, LSB)补零。对逻辑右移操作,需要在最高有效位(Most Significant Bit, MSB)补零。而对算术右移操作,则需要在高位做符号位扩展。同时,为了指令集的简洁,RV32I中没有包括循环移位指令,因为循环移位可以通过移位指令和其他指令的组合来实现。

| <u>31</u> | 0000000 | <u>25</u> | <u>24</u><br>移位   | <u>20</u><br>:量 | <u>19</u> <u>1</u><br>源寄存器 | 5 <u>14</u>        | 001      | <u>12</u> | 11 <u>11</u> 目标寄存器 | 7 6        | 0010011 | 0        | SLLI | 立即数逻辑左移 |

|-----------|---------|-----------|-------------------|-----------------|----------------------------|--------------------|----------|-----------|--------------------|------------|---------|----------|------|---------|

| 31        |         | 25        | 24                | 20              | 19 1                       | <br>5 14           |          | 12        | 11 7               | 7 6        |         | <u>0</u> |      |         |

|           | 0000000 |           | <del></del><br>移位 |                 | 源寄存器                       |                    | 101      | <u></u>   | 目标寄存器              |            | 0010011 |          | SRLI | 立即数逻辑右移 |

| <u>31</u> |         | <u>25</u> | <u>24</u>         | <u>20</u>       | <u>19</u> <u>1</u>         | <u>5</u> <u>14</u> | <u> </u> | <u>12</u> | . <u>11</u>        | <u>7 6</u> |         | 0        |      |         |

|           | 0100000 |           | 移位                | 量               | 源寄存器                       | 1                  | 101      |           | 目标寄存器              |            | 0010011 |          | SRAI | 立即数算术右移 |

图3-9 立即数移位操作

## 第3章 RISC-V 指令集

SRLI与 SRAI 的唯一编码区别是第 30 位。在处理器硬件实现上述移位指令时,硬件只需判断此位便可加以区分。然而,为了兼容性测试的需要,RISC-V 官方提供了一个非法指令(Illegal Instruction)的软件测试,当硬件遇到非法指令时产生异常。为了通过该测试,硬件设计时需要将图 39 中的高 7 位都考虑进去。

#### 5)32位立即数构建与地址生成

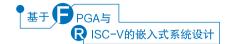

通过对图 3-5 的观察可以发现,U-TYPE 指令中的立即数有 20 位,而 I-TYPE 指令中的立即数有 12 位。32 位立即数可以通过一条 U-TYPE 指令和一条 I-TYPE 指令来联合构建。图 3-10 中的 LUI(Load Upper Immediate,高位立即数载入)指令即是为此目的而设计的,该指令会将其所携带的 20 位立即数载入目标寄存器的高位,而将目标寄存器的低 12 位置零。如果在 LUI 指令之后紧随一条 ADDI 指令,则可以继续构建目标寄存器的低 12 位,从而拼接出完整的 32 位立即数。该 32 位立即数也可以作为 32 位的地址使用。

图3-10 立即数和立即地址构建指令

根据 RISC-V 这种 "20+12=32" 的立即数指令格式,可以把 RISC-V 的内存空间想象成一个分页的结构,其每个页面的大小为 2<sup>12</sup>=4 096 字节,而页地址则有 20 位。图 3-10 中的 AUIPC(Add Upper Immediate to PC,高位立即数加 PC)指令就是为了移动页地址而设计的,和其他的 U-TYPE 指令一样,AUPIC 也会将其携带的 20 位立即数作为高位,而将低 12 位置零,以生成一个完整的 32 位数。然后该32 位数会与当前指令计数器(32 位寄存器)的值相加,并将结果存入目标寄存器(RV32I 也用 PC 来存放当前活跃指令的内存地址)。

RISC-V的设计目标之一就是为高级语言提供硬件支持,而有了AUIPC指令,可以很容易构建相对PC的寻址方式,从而实现独立于地址的代码(Position Independent Code, PIC)。如果要将相对于当前地址0x1234字节的内容载入x4寄

存器,则可以通过 AUIPC 指令用如下的代码实现:

```

aupic x4, 0x1 # PC + 0x1000 => x4

lw x4, 0x234(x4) # (x4 + 0x234) => x4

```

如果不使用 AUIPC 指令,则需要采用如下的变通办法:

虽然上面的变通办法也可以达到目的,但是它有以下缺点:

- (1)代码晦涩冗长,而且需要借助额外的寄存器 x5。

- (2)跳转指令(Jump and Link, JAL)可能会误导流水线的运行,使得流水线执行清空动作。在某些采用 BTB(Branch Target Buffer,分支目标缓冲区)(用来记录之前发生过跳转的指令的 PC 值和目标地址)来做跳转预测的处理器上,上面的跳转指令会在 BTB 中留下记录条目,但对跳转预测却并无帮助,因为目标地址等同于下一条顺序执行的指令地址。

由此可见, AUIPC 的引入极大地减轻了编译器的负担。

#### 注解: 跳转预测

为了进一步提高流水线的运行效率,处理器的设计者往往会在取指器中加入跳转预测的模块。跳转预测常用的模块部件有:

- ① BHT (Branch History Table, 跳转历史表),利用 PC 的末几位地址,来记录之前发生的跳转历史,作为动态跳转预测的依据。BHT 有时也叫 BHB (Branch History Buffer)。

- ②BTB, 当跳转发生时, BTB 会记录下跳转指令的地址和其目标地址 (Target Address)。当该 PC 值再次被遇到时,则可以将之前记录的目标地址

88

## 第 3 章 RISC-V 指令集

作为指令读取的地址。一般来讲,最终真正的目标地址都会在流水线比较靠后的阶段才能确定,如果最后确定的目标地址与之前记录的地址不一致,则宣告跳转预测失败,清空流水线重新取指令。否则,预测成功,流水线不会有停顿。

③ RAS (Return Address Stack, 返回地址栈), RAS与BTB有些类似, RAS主要是用来对跳转返回指令提供预测地址。当程序遇到函数调用指令时, 会把函数的返回地址存入 (push) 到 RAS中。当取指器认为当前指令是一条跳转返回指令时,就会做退栈动作 (pop),并把之前存在 RAS 栈顶的地址作为下一条指令的读取地址。之后,在流水线比较靠后的阶段,当最终的目标地址被确定时,如果目标地址与 RAS 提供的预测地址不吻合,则预测失败,清空流水线重新取指令;否则,预测成功,流水线不会有停顿。

#### 2. 寄存器 - 寄存器指令

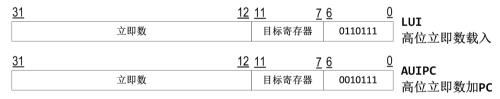

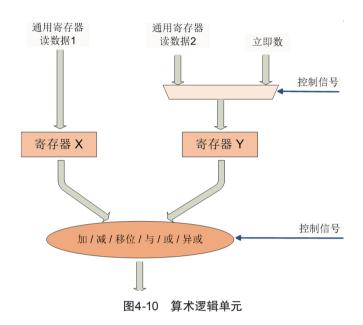

寄存器 - 寄存器指令包括加减法(见图 3-11)、数值比较(见图 3-12)、逻辑操作(见图 3-13)与移位操作(见图 3-14)。这些指令的功能和前面的立即数指令相似,唯一的区别是立即数指令中的立即数被替换为源寄存器 2(寄存器 - 寄存器指令中包含减法指令,而立即数操作则没有定义减法)。

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7   | <u> </u> | 0 | SLT寄存器  |

|-----------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|-----------|-----|----------|---|---------|

|           | 0000000 |           | 源寄        | 存器2       | 源         | 寄存器1      |           | 010 |           | 目标寄存器     |     | 0110011  |   | 符号数比较   |

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7 9 | <u> </u> | 0 | SLTU寄存器 |

|           | 0000000 |           | 源寄        | 存器2       | 源         | 寄存器1      |           | 011 |           | 目标寄存器     |     | 0110011  |   | 无符号数比较  |

图3-12 寄存器数值比较

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | <u>7</u> | <u>6</u> | 0 |            |

|-----------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|-----------|----------|----------|---|------------|

|           | 0000000 |           | 源寄存       | 字器2       | 源寄存       | 器1        |           | 111 |           | 目标寄存器     |          | 0110011  |   | AND寄存器逻辑与  |

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7        | <u>6</u> | 0 |            |

|           | 0000000 |           | 源寄存       | 字器2       | 源寄存       | 器1        |           | 110 |           | 目标寄存器     |          | 0110011  |   | OR寄存器逻辑或   |

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | <u>7</u> | <u>6</u> | 0 |            |

|           | 0000000 |           | 源寄存       | 字器2       | 源寄存       | 器1        |           | 100 |           | 目标寄存器     |          | 0110011  |   | XOR寄存器逻辑异或 |

图3-13 寄存器逻辑操作

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u> 19</u> | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7 9 | <u>S</u> | 0 |            |

|-----------|---------|-----------|-----------|-----------|------------|-----------|-----------|-----|-----------|-----------|-----|----------|---|------------|

|           | 0000000 |           | 源寄存       | 字器2       | 源寄         | 存器1       |           | 001 |           | 目标寄存器     | \$  | 0110011  |   | SLL寄存器逻辑左移 |

| 31        |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u>  | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7 9 | <u> </u> | 0 |            |

|           | 0000000 |           | 源寄存       | 字器2       | 源寄         | 存器1       |           | 101 |           | 目标寄存器     | \$  | 0110011  |   | SRL寄存器逻辑右移 |

| <u>31</u> |         | <u>25</u> | <u>24</u> | <u>20</u> | <u>19</u>  | <u>15</u> | <u>14</u> |     | <u>12</u> | <u>11</u> | 7 9 | <u> </u> | 0 |            |

|           | 0100000 |           | 源寄存       | 字器2       | 源寄         | 存器1       |           | 101 |           | 目标寄存器     | \$  | 0110011  |   | SRA寄存器算术右移 |

图3-14 寄存器移位操作

由于这些相似性,本书对寄存器 - 寄存器指令不再赘述,读者如有疑问,可以查阅 RISC-V 官方标准中的相关部分。

## 3.4.6 控制转移指令

RISC-V 中的转移控制指令(Control Transfer Instructions)主要包括以下两类:

- (1) 无条件跳转(Unconditional Jump)。

- (2) 有条件跳转(Conditional Branches)。

不过和其他指令集相比, RISC-V 的跳转指令设计得非常有特色:

- (1) RISC-V 中并没有专门的函数调用指令,函数的调用是通过设置跳转指令中的寄存器来实现的,这样减小了指令集的规模。

- (2) RISC-V 将比较和跳转相结合,而且利用条件跳转来对"溢出""零

值"等做出判断。RISC-V本身并不专设状态寄存器来做溢出位、加法进位、 零值标识等,从而简化了处理器结构。

(3) RISC-V 为无条件跳转指令专门定义了一种 J-TYPE 的指令格式,而该格式衍生于 U-TYPE。J-TYPE 只是在 U-TYPE 的基础上,对立即数的某些位做了位置调整。对有条件跳转指令,RISC-V 也做了类似的处理,在 S-TYPE 的基础上衍生出了 B-TYPE。这些细微的调整,可以在一定程度上降低硬件设计的开销。

#### 1. 无条件跳转指令 (Unconditional Jump)

1) 直接跳转 JAL (Jump and Link, 跳转与链接)

JAL 指令如图 3-15 所示。RISC-V 为 JAL 指令专门定义了 J-TYPE 格式。将图 3-15 和图 3-5 中的 U-TYPE 比较,可以发现除了立即数的某些位做了位置调整以外,其他都没有变化。JAL 指令会把其携带的 20 位立即数做符号位扩展,并左移一位,产生一个 32 位的符号数。然后将该 32 位符号数和 PC 相加来产生目标地址(这样,JAL 可以作为短跳转指令,跳转至 PC ± 1 MB 的地址范围内)。

| <u>31</u> | <u>30</u> | <u>21</u> | <u>20</u> | <u>19</u> | <u>12</u> | <u>11</u> | <u>7 6</u> | <u>0</u> | 741 (7 TVDE)        |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------------|----------|---------------------|

| 立即数[20]   | [10:1]    |           | [11]      | [19       | :12]      | 目标寄存器     | 1101111    |          | JAL(J-TYPE)<br>直接跳转 |

|           |           |           |           | 图2_       | 15 L      | NI 华仝     |            |          | 且按购权                |

同时,JAL 也会把紧随其后的那条指令的地址存入目标寄存器中。这样,如果目标寄存器是零,则JAL等同于GOTO指令;否则,JAL可以实现函数调用的功能。

2) 间接跳转 JALR (Jump and Link Register, 跳转与链接寄存器)

JALR 指令如图 3-16 所示。JALR 指令会把所携带的 12 位立即数和源寄存器相加,并把相加的结果末位清零,作为新的跳转地址。同时,和 JAL 指令一样,JALR 也会把紧随其后的那条指令的地址存入目标寄存器中。

| <u>31</u> | <u>20 19</u> | <u>15</u> | <u>14</u> | <u>12</u> | <u>76</u> | <u>0</u> | JAI R        |

|-----------|--------------|-----------|-----------|-----------|-----------|----------|--------------|

| 立即数[      | 11:0] 源      | 寄存器1      | 000       | 目标寄存      | 器         | 1100111  | JALK<br>间接跳转 |

图3-16 JALR指令

JAL 指令受其指令格式所限,只能实现 PC±1 MB 的短跳转。而通过如下的指令序列将 JALR 指令和 LUI/AUIPC 指令相结合,可以实现全地址空间的跳转:

lui ra, 立即数(20位) jalr ra, ra, 立即数(12位) 或者

> auipc ra, 立即数(20位) jalr ra, ra, 立即数(12位)

#### 2. 动态预测返回地址

尽管 RISC-V 指令集本身并没有对 JAL 或 JALR 中目标寄存器的取值做出限制,但是根据前面提到的函数调用约定(Calling Convention),JAL/JALR 常用的目标寄存器有 x1 (ra, 返回地址)和 x5 (t0, 替代链接寄存器)。对普通的函数调用,x1 (ra) 会被用来存放返回地址。然而,表 3-1 的调用约定中还定义了 x5 (替代链接寄存器),其作用是:

- (1) 在使用压缩扩展指令集(Compressed Instruction Extension)时,方便将函数调用的开场白和收场白作为公共的函数调用,从而到达提高代码密度(Code Density)的目的。对 x5(替代链接寄存器)的具体用法,会在后续有关"压缩指令扩展"的章节做详细讨论。

- (2)对于协程(Coroutine)这种需要实现堆栈切换的情况,利用 x5(替代链接寄存器)可以帮助实现快速的 Coroutine 调用与返回(见表 3-2)。

表 3-2 JALR 指令的 RAS 操作

| 目标寄存器(rd)                        | <br>  源寄存器(rs1)                  | rd ?= rs1 | RAS操作 | 备注                           |

|----------------------------------|----------------------------------|-----------|-------|------------------------------|

| $(rd \neq x1) \&\& (rd \neq x5)$ | $(rs1 \neq x1) && (rs1 \neq x5)$ | 无关        | 无     | 非 函 数 调 用<br>指令,亦非调<br>用返回指令 |

续表

| 目标寄存器(rd)                        | 源寄存器(rs1)                          | rd ?= rs1  | RAS操作                   | 备 注    |

|----------------------------------|------------------------------------|------------|-------------------------|--------|

| $(rd \neq x1) \&\& (rd \neq x5)$ | (rs1 = x1)   <br>(rs1 = x5)        | 无关         | 返回地址<br>出栈              | 调用返回指令 |

| (rd = x1)   <br>(rd = x5)        | $(rs1 \neq x1) \&\& (rs1 \neq x5)$ | 无关         | 返回地址<br>入栈              | 函数调用指令 |

| (rd = x1)   <br>(rd = x5)        | (rs1 = x1)   <br>(rs1 = x5)        | (rd ≠ rs1) | 在同一指令<br>周期中,既<br>出栈又入栈 | 协程     |

| (rd = x1)   <br>(rd = x5)        | (rs1 = x1)   <br>(rs1 = x5)        | (rd = rs1) | 返回地址<br>入栈              | 宏操作合并  |

RISC-V的函数调用约定将 JAL/JALR 在调用和返回时可使用的寄存器限制在 x1 或 x5 上,为动态预测返回地址创造了条件。在 3.4.5 节的注解部分,提到了跳转预测常用的三种模块:BHT、BTB 与 RAS。将 RAS 与无条件跳转指令相结合,则可以很好地实现返回地址的动态预测,具体做法如下:

### (1) JAL 指令的 RAS 操作。

根据函数调用约定,当 JAL 的目标寄存器值是 x1 或者 x5 时,可以判定其是在做函数调用。这时可以把返回地址(紧随其后的那条指令的地址)压入 RAS。

#### (2) JALR 指令的 RAS 操作。

JALR 指令既可以作为函数调用指令,又可以作为调用返回指令,其 RAS 的操作方式如表 3-2 所示。

#### 注解: 协程

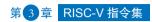

在多任务处理中(Multi-task),协程(Coroutine)可以被看作一种合作式(Collaborative),非抢断式(Non-preemptive)的线程(Thread)。图 3-17 展示了两个协程互相调用的情形,其中每一个节点都是一个退让(Yield)操作。这样的话,协程 A 和 B 会轮流按照 1、2、3、4、5 的顺序执行。

图3-17 协程

为了实现协程,往往需要做堆栈的切换。把 alternative link register和表 3-2 相结合,把 x1(ra)与 x5 (替代链接寄存器)分别分配给图 3-17中的协程 A 和 B,则可以提高跳转预测的准确率,以实现协程的快速调用和返回。在图 3-17中除第一个退让外,其他的退让操作既可以看作从一个协程返回另外一个协程,又可以看作从一个协程调用另外一个协程。这就是为什么表 3-2 中的第 4 行既有出栈操作,又有入栈操作。

## 注解:宏操作合并

在处理器设计中,可以设计一个硬件模块,在指令解码阶段之前,通过对已取指令序列的观察,将其中某些前后相邻的简单指令合并为一条复杂的指令(可以是处理器内部定义的专门指令),以提高指令执行效率,这种做法称为宏操作合并(Macro-Op Fusion)。3.4.6 节最后所提到的 LUI+JALR 或AUIPC+JALR 指令序列,就是被宏操作合并的典型例子。表 3-2 中的最后一行,就是为了提高这两个指令序列被宏操作合并之后的跳转预测准确率而设计的。

这里要注意的是,宏操作合并是处理器设计实现的方法,与指令集本身 无关。另外, Intel 公司是宏操作合并技术的发明者,对该项技术拥有专利。

#### 3. 条件编码

在讨论有条件跳转指令(Conditional Branches)之前,有必要先介绍一下条件编码(Condition Code)的概念。实际上,以笔者多年从事嵌入式设计的经验来看,由于各种技术指标之间的相互抵触(例如数字设计的 $AT^2$ 边界限制),设计的过程更多的是在各个技术方案之间寻求妥协和取舍,以求达到总体最优的过程。RISC-V 的设计者也是基于各种综合的考量,最终决定舍弃条件编码,而代之以将

条件判断与跳转指令直接相结合的方案, 具体如下。

在传统的 RISC 设计中,设计者往往会安排一个状态寄存器,在其中放置各类的标志位 [例如溢出标志(Overflow)、零标志(Zero Flag)、进位标志(Carry)等]。在某条指令更改了这些标志位之后,后续的指令会根据更改后的标志位来决定是否需要被执行。为此,这些标志位会被编码(即条件编码),并成为指令编码的一部分。

在 ARMv8 指令集中,就在指令编码中专门分配了 4 位,用来做条件编码,以表示比较相等(结果为零)、溢出等状态。对" if (a==10)  $\{\cdots\}$ "这样的高级代码,编译器的常用处理方式是在一个计算指令之后跟随一个条件执行指令,如下面的伪代码所示:

subtraction (register - 10) branch if zero flag is not set

- # 减法,结果可以被丢弃

- # 如果不相等则跳转

<u>注意</u>:上面的代码序列实际上包含了状态寄存器的使用。第一条的减法指令会影响状态寄存器中的零标志位,而第二条的跳转指令中的条件编码包含有零标志判断,但是不包含对通用寄存器的读取。

使用条件编码的优点是可以让条件跳转指令变得相对比较简单(不涉及对通用寄存器的读取,只涉及标志位),这样跳转条件就可以在流水线比较靠前的阶段被判断出来。但是这样做的缺点是条件编码需要在指令编码中占用一定的位,而且需要在条件跳转指令之前安排另外一条指令用来设置标志位,降低了代码密度。同时,硬件也需要有专门的状态寄存器,记录各种标志位。

而 RISC-V 的设计者则另辟蹊径,将上面标志位设置指令合并到条件跳转指令中去,在条件跳转指令中直接读取通用寄存器做判断,这种做法的优点是:

- 没有条件编码,节省下的位可以被指令编码派作其他用途,从而减小指令 集规模。

- 只要一条指令就可以实现上面需要两条指令来实现的功能,提高了代码密度。

- 不需要专门的状态寄存器来记录各种标志位,降低了硬件的开销。

这种做法的缺点是:由于需要在条件跳转指令中直接读取通用寄存器,跳转条件要在流水线中比较靠后的阶段才能判定。RISC-V的设计者认为,目前跳转预测的准确度(预测跳转是否发生)和精确度(预测跳转目标地址)都已经大幅提高,将跳转条件的判定在流水线中后移并不会给性能带来太大的负面影响。权衡利弊,RISC-V最终还是舍弃了条件编码。

#### 4. 有条件跳转指令

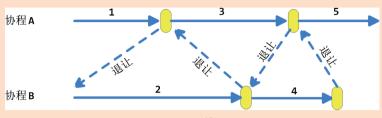

RV32I的有条件跳转指令总共有6条,其定义如图3-18所示(图中网格标记的深色部分为立即数)。RISC-V为有条件跳转指令专门定义了新的指令格式B-TYPE,其衍生于图3-5中的S-TYPE。通过将图3-18与图3-5中的S-TYPE作比较,可以发现B-TYPE只是在S-TYPE的基础上对立即数的某些位做了顺序调整,其原因会在后续章节讨论。

图3-18 有条件跳转指令

有条件跳转指令会将源寄存器 1 中的值和源寄存器 2 中的值做比较,如果满足表 3-3 中的比较条件则跳转,其目标地址产生的办法如下:

有条件跳转指令会把其携带的 12 位立即数做符号位扩展,并左移 1 位,来产生一个 32 位的立即数。该立即数会和当前的程序计数器值相加,来产生最终的目标地址。这样的话,有条件跳转指令能跳转至 PC±4 KB 的地址范围内。

表 3-3 有条件比较跳转指令

| 有条件跳转指令 | 跳转条件                  | 备注     |

|---------|-----------------------|--------|

| BEQ     | (源寄存器 1) = (源寄存器 2)   | _      |

| BNE     | ( 源寄存器 1) ≠ ( 源寄存器 2) | _      |

| BLT     | (源寄存器 1) < (源寄存器 2)   | 有符号数比较 |

| BLTU    | (源寄存器 1) < (源寄存器 2)   | 无符号数比较 |

| BGE     | ( 源寄存器 1) ≥ ( 源寄存器 2) | 有符号数比较 |

| BGEU    | ( 源寄存器 1) ≥ ( 源寄存器 2) | 无符号数比较 |

另外,将源寄存器 1 和源寄存器 2 对换,则可以从表 3-3 里的最后 4 条指令产生另外 4 条衍生指令,即 BGT(符号数比较,大于则跳转)、BGTU(无符号数比较,大于则跳转)、BLEU(无符号数比较,不大于则跳转)。

#### 5. 静态跳转预测

RISC-V的设计者没有使用条件编码,而是选择让有条件跳转指令(Conditional Branches)直接对寄存器进行比较,导致跳转条件要在流水线中比较靠后的阶段才能判定。为了减少这种设计策略对处理器性能的负面影响,RISC-V对跳转预测非常重视。除了动态跳转之外,针对有条件跳转指令,RISC-V还对软硬件设计者做出了如下的建议,以帮助提高静态跳转的准确率:

- (1) 在软件设计中不要用条件永远为真的有条件跳转指令(例如 BEQ x0, x0) 来代替无条件跳转指令,以减少对分支预测不必要的干扰。

- (2)对于有条件跳转指令,其顺序分支应存放比较常用的代码,而其跳转发展应存放不太常用的代码。对高级语言的循环指令来说,这意味着循环体应放在顺序分支上。

- (3)和高级语言的循环指令相关的另外一条对处理器硬件设计的建议就是:对于向前跳转的指令(目标地址大于 PC),应静态预测该跳转不发生。对向后跳转的指令(目标地址小于 PC),应静态预测该跳转会发生。如果和上一条建议相结合使用的话,则这种静态预测的策略非常符合大多数循环体

的实际状况(重复 N次,然后退出循环)。软件设计者在做优化设计时,也应该将此条考虑在内。对有条件跳转指令,由于目标地址的产生非常简单直接(PC+ 立即数),所以不需要很大的硬件开销就可以实施这条指令。

#### 6. B-TYPE 和 J-TYPE 中的立即数

RV32I 中为 JAL 指令和有条件跳转指令分别定义了 J-TYPE 与 B-TYPE 格式。这两种格式实际上各自衍生于 U-TYPE 与 S-TYPE。J-TYPE 除了立即数的位排列与 U-TYPE 不一样外,其他的格式都与 U-TYPE 一样。B-TYPE 也是通过类似的方式衍生于 S-TYPE。RISC-V 的设计者做出这种安排的主要原因是为了减小硬件的开销,现说明如下。

为了实现 16 位地址的边界对齐,JAL 指令和有条件跳转指令都需要将其所携带的立即数做左移一位的操作。如果不在指令格式上做些处理的话,那么最后生成的 32 位立即数,其位的位置和 U-TYPE 与 S-TYPE 相比,会因位置的偏差而没有对齐,这就会增加指令解码器的硬件开销。而衍生定义 J-TYPE 和 B-TYPE 的目的,就是为了将移位后的大部分位保留在原来的位置上。

将图 3-5 中的 I-TYPE、S-TYPE 和 U-TYPE 与图 3-15 及图 3-18 做比较,可以将处理器中有关 32 位立即数生成的各位组成归纳如表 3-4 所示。

立即数位

对应的指令位

[31]

位 31

[30:20]

I-TYPE, S-TYPE, B-TYPE: 位 31 的符号位扩展

[19:12]

I-TYPE, S-TYPE, B-TYPE: 位 31 的符号位扩展

U-TYPE, J-TYPE:[19:12]

[11]

B-TYPE: 位 7

J-TYPE: 位 20

U-TYPE: 数值零

表 3-4 立即数位组成

续表

| 立即数位   | 对应的指令位                                 |

|--------|----------------------------------------|

| [10:5] | I-TYPE, S-TYPE, B-TYPE, J-TYPE:[19:12] |

| [10:5] | U-TYPE: 数值零                            |

| [4:1]  | I-TYPE, J-TYPE:[24:21]                 |

|        | S-TYPE, B-TYPE:[11:8]                  |

|        | U-TYPE: 数值零                            |

|        | I-TYPE: 位 20                           |

|        | S-TYPE: 位7                             |

|        | B-TYPE, U-TYPE,S-TYPE: 数值零             |

从表 3-4 可以看出,在最终需要产生的 32 位立即数中,有多于 80%的位(26/32) 其来源最多只有两个,从而极大降低了立即数生成的硬件开销。而这一优势,都是 拜衍生格式 B-TYPE 与 J-TYPE 所赐。

## 3.4.7 内存载入与存储指令

#### 1. 小端模式

对于字长超过 8 位的系统,其数据在内存中的存放方式主要有两种:一种是小端模式(Little Endian,小字节序或低字节序),即对每个字长的数据,将低位的字节存放在内存地址的低位部分;另外一种存放方式是大端模式(Big Endian,大字节序或高字节序),即对每个字长的数据,将高位的字节存放在内存地址的低位部分。虽然从技术角度来说,这两种存放方式各有利弊,但是考虑到目前大部分的商用系统都采用小端模式,所以 RISC-V 的设计者也决定将小端模式定为 RISC-V 的标准模式。

#### 2. 载入指令

和传统的 RISC 指令集一样,RISC-V 避免了 CISC 指令集中那种通过多种寻址方式 访问内存的做法,而将内存的访问仅限于载入(Load)和存储(Store)指令。RISC-V 中 的内存载入指令包括单字节、双字节和 32 位三种字长。同时对单字节和双字节指令,根据其符号位处理方式的不同(符号位扩展或零位填充),又可分为符号数载入与无符号数载入。为此,RISC-V 中定义了 5 条不同的载入指令,如图 3-19 所示。

| <u>31</u> |           | <u>20</u> | <u>19</u> <u>15</u>                  | <u>14</u> |     | <u>12</u> | <u>11</u>   | <u>76</u>         |         | <u>0</u> | I.D.             |

|-----------|-----------|-----------|--------------------------------------|-----------|-----|-----------|-------------|-------------------|---------|----------|------------------|

|           | 立即数[11:0] |           | 源寄存器1                                |           | 000 |           | 目标寄存器       |                   | 0000011 |          | LB<br>单字节符号数载入   |

| <u>31</u> | 立即数[11:0] | <u>20</u> | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | <u>14</u> | 100 | <u>12</u> | 11 目标寄存器    | <u>7 6</u>        | 0000011 | 0        | LBU<br>单字节无符号数载入 |

| <u>31</u> | 立即数[11:0] | <u>20</u> | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | 14        | 001 | <u>12</u> | 11 目标寄存器    | <u>7 6</u>        | 0000011 | 0        | LH<br>双字节符号数载入   |

| <u>31</u> | 立即数[11:0] | <u>20</u> | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | <u>14</u> | 101 | <u>12</u> | 11<br>目标寄存器 | <u>7 6</u>        | 0000011 | 0        | LHU              |

| <u>31</u> |           | <u>20</u> | <u>19</u> <u>15</u>                  | 14        |     | <u>12</u> | <u>11</u>   | <u>7</u> <u>6</u> |         | 0        | 双字节无符号数载入<br>LW  |

|           | 立即数[11:0] |           | 源寄存器1                                |           | 010 |           | 目标寄存器       |                   | 0000011 |          | 32位符号数载入         |

图3-19 内存载入指令

在图 3-19 所示的内存载入指令中,需要将其所携带的 12 位立即数作符号扩展,变为一个 32 位的符号数,然后将该 32 位符号数同源寄存器相加,以产生内存的读取地址。内存读取完成后,从内存读取的数据最终会被存入目标寄存器。

内存的读取可能会导致硬件异常, 具体的细节会在后续章节讨论。

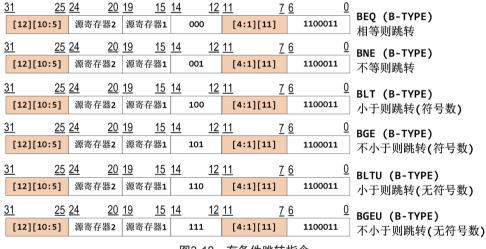

#### 3. 存储指令

和载入指令相类似,RISC-V 中还根据字长的不同,分别定义了三种内存存储指令,如图 3-20 所示。其内存写入地址的产生也和载入指令类似,即将其所携带的 12 位立即数作符号扩展并同源寄存器 1 相加。而需要写入内存的数据则存放于源寄存器 2 当中。

图3-20 内存存储指令

同内存读取一样,内存的写入操作也可以导致硬件异常。

## 4. 非对齐的内存读写 (Misaligned Memory Access)

和许多其他的系统一样,内存读写地址都是字节地址,如果软件操作不慎,就可能引起非对齐的内存读写,导致内存操作无法在一个读写周期内完成。对于这种情况,RISC-V中并没有强制规定应对之道,而是交由处理器的设计者来自行决定。通常来说,处理器的设计者可以有硬件处理和软件处理两种解决策略。

- (1)处理器的设计者可以选择以硬件方式来处理非对齐的内存读写,除了增加硬件开销之外,还需要考虑读写操作的原子化问题。由于非对齐的内存读写往往需要两个读写周期才能完成,如果处理器硬件在设计时不加以特殊处理,则可能会由于外部中断等原因,导致在这两个读写周期之间被插入其他的操作,使内存读写不再是一个原子化的操作。RISC-V本身对这种情况并没有做强制规定,而是由软硬件开发者自行决定。

- (2)处理器的设计者也可以选择不在硬件层面去处理,而代之让硬件产生异常,然后交由软件处理。

## 3.4.8 RV32I 内存同步指令

RISC-V的设计者在设计之初就考虑到了并行处理的问题,在RISC-V的术语中,每个处理器核可以包含多个硬件线程,称作硬件线程(Hardware Thread,HART)。每个HART都有自己的程序计数器和寄存器空间,独立顺序运行指令。不同的HART会共享同一个内存地址空间,从这一点上来说,HART和Intel处理器中的超线程(Hyper Thread)非常类似。

在 RISC-V 中,当这些不同的 HART 需要做内存访问同步时,需要显式地(Explicitly)使用 FENCE 指令来同步数据。由于多 HART 的问题不在本书讨论的范围之内,所以本书对 FENCE 指令不再做进一步阐述。然而,即使是顺序执行指令的单核单硬件线程处理器,其也会有内存同步的问题,具体主要有以下两种情形:

- (1)自修改代码(Self-modifying Code),即程序在执行过程中,会动态修改自己的指令存储内存。无论在工业界还是学术界,这种做法都是颇有争议的。甚至有些极端的看法认为只有病毒软件才需要自修改代码,而且自修改代码往往会带来安全上的隐患,所以不建议使用。

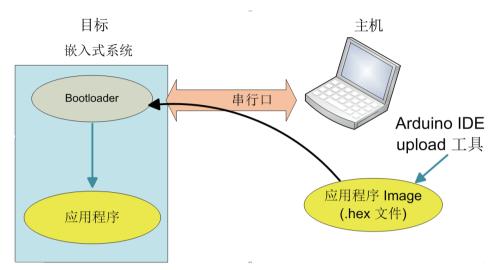

- (2)软件载入过程。软件载入的一般情况是处理器上电后会先运行引导加载程序(Bootloader),然后引导加载程序会把其他软件当作数据载入到内存中,接着跳转至载入地址,运行新载入的软件。在这个过程当中,处理器可能存在指令内存预读取、指令缓存、流水线等一系列对内存同步有复杂影响的活动,在新软件被运行之前,需要采取措施,以保证内存同步。

不论是上面哪一种情况,为了实现内存同步,处理器都先要运行某个固定的指令序列来清空缓存、刷新流水线等。这个固定的指令序列被称作内存屏障(Memory Barrier)。内存屏障通常是由处理器设计者提供给软件设计者的。在RISC-V中,定义了指令同步命令FENCE.I(该指令属于Zifencei扩展),用来发挥内存屏障的作用。

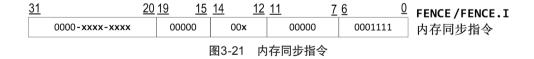

由于本书只讨论单处理核的情况,所以在本书所涉及的范围内,FENCE 与FENCE.I 的实现并没有太大的区别,其定义如图 3-21 所示。

## 3.4.9 控制与状态寄存器指令

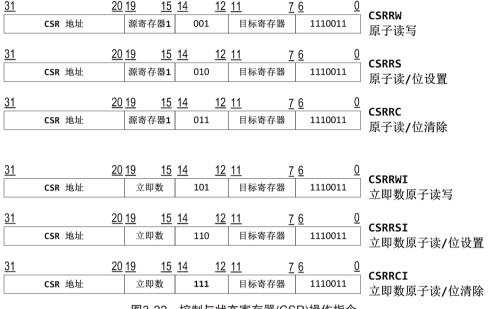

RISC-V 中除了内存地址空间和通用寄存器地址空间外,还定义了一个独立的控制与状态寄存器(Control Status Register, CSR)地址空间,其地址宽度是 12 位。随着设计目标的不同,每个处理器实际实现的 CSR 可能会有所不同,因此RISC-V 将 CSR 的定义放在了特权架构部分,不过这些 CSR 的访问方式却是一致的,RISC-V 将访问这些 CSR 的指令定义在了用户指令集中(Zicsr 指令集扩展)。

如图 3-22 所示, RISC-V 中一共定义了 6 条访问 CSR 的命令, 其具体功能

102

如表 3-5 所示。

图3-22 控制与状态寄存器(CSR)操作指令

表 3-5 CSR 命令的功能定义

| 指令     | 功能                                    |

|--------|---------------------------------------|

| CSRRW  | (CSR)→(目标寄存器); (源寄存器 1)→(CSR)         |

| CSRRS  | (CSR)→(目标寄存器); (CSR) (源寄存器 1)→(CSR)   |

| CSRRC  | (CSR)→(目标寄存器); (~(CSR))&(源寄存器1)→(CSR) |

| CSRRWI | (CSR)→(目标寄存器); 立即数→(CSR)              |

| CSRRSI | (CSR)→(目标寄存器); (CSR) 立即数→(CSR)        |

| CSRRCI | (CSR)→(目标寄存器); (~(CSR))&立即数→(CSR)     |

在表 3-5 中定义的这些命令还包含如下规定:

- (1)表 3-5 中定义的操作都是原子操作。

- (2)对从 CSR 中读取的值都应该做零位扩展(将高位未使用部分置零)。

- (3)对立即数,也应将未使用的高27位置零。

103

- (4) 如果目标寄存器为 x0 的话,则 CSRRW 和 CSRRWI 应避免读取 CSR,避免产生不必要的副作用。

- (5) 如果源寄存器为 x0,则 CSRRS、CSRRC 应避免对 CSR 写入操作。

- (6) 如果立即数为零,则 CSRRSI、CSRRCI 应避免对 CSR 写入操作。

在具体实现时,上述的这6条指令可以由硬件实现,也可以为了减小硬件开销, 而选择让硬件产生异常,转而由软件来处理。

## 3.4.10 环境调用与软件断点

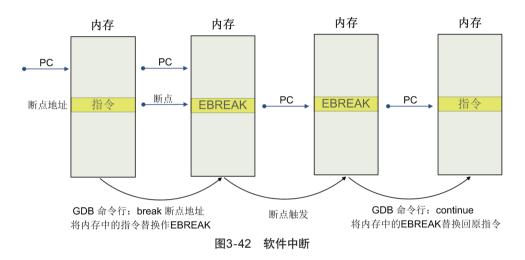

如图 3-23 所示, RISC-V 中还定义了两条指令(ECALL 和 EBREAK),以实现操作系统的系统调用与软件断点。

| <u>31</u> |             | <u>20</u> | <u>19</u> <u>15</u> | <u>14</u> | <u>12</u> | <u>11</u> | <u>7</u> | <u>6</u> | 0 |               |        |

|-----------|-------------|-----------|---------------------|-----------|-----------|-----------|----------|----------|---|---------------|--------|

|           | 00000000000 |           | 00000               |           | 000       | 00000     |          | 1110011  |   | ECALL         | 环境调用指令 |

|           |             |           |                     |           |           |           |          |          |   |               |        |

| <u>31</u> |             | <u>20</u> | <u>19</u> <u>15</u> | <u>14</u> | <u>12</u> | <u>11</u> | <u>7</u> | <u>6</u> | 0 |               |        |

|           | 00000000001 |           | 00000               |           | 000       | 00000     |          | 1110011  |   | <b>EBREAK</b> | 软件断点指令 |

图3-23 环境调用与软件断点指令

## 3.4.11 基础指令集的面积优化方案

RV32I中共包含47条指令,分为6类,其各类包含的指令条目数如表3-6所示。

|          | 衣 3-0 RV32I 拍マ宋日数                |

|----------|----------------------------------|

| 指令       | 指令数                              |

| 算术逻辑指令   | 立即数指令 (11) + 寄存器-寄存器指令 (10) = 21 |

| 跳转指令     | 无条件跳转指令(2)+有条件跳转指令(6)=8          |

| 内存存储指令   | Load (5) + Store (3) = 8         |

| FENCE 指令 | 2                                |

| CSR 指令   | 6                                |

| 环境调用与断点  | 2                                |

表 3-6 RV32I 指今条目数

如果处理器设计者想要极力减小硬件逻辑开销,可以选择性地将表 3-6 中最后的 3 类共 10 条指令做简化实现,即将 FENCE 指令用 NOP 来代替,将 CSR 指令和 ECALL、EBREAK 合并解码(这些指令的操作码部分都是一样的)并产生异常,然后交由软件处理。这样的话,指令集实际需要实现的总指令数变为 47-2-6-2+1=38 条。对面积(Area)优化的处理器设计,可以采取这种简化的方案。

# 3.5 RISC-V扩展指令集

RISC-V 将指令集分成基础指令集和扩展指令集(Extension)。基础指令集已 经在前文中得到阐述,而扩展指令集则有 M (乘除法扩展)、C (压缩指令扩展)、A (原子操作扩展)、F (单精度浮点扩展)、D (双精度浮点扩展)等众多的标准扩展。除此之外,RISC-V 还允许处理器设计者添加非标准的扩展。

由于扩展众多,在编译器编译代码时,需要把目标处理器具体支持的指令扩展告诉编译器。以 GCC (GNU C Compiler)为例,其在编译代码时,往往需要软件工程师提供以下两个选项:-march 和-mabi。

- (1)-march 选项被用来告知 GCC 目标处理器的基础指令集和扩展,对 32 位基础指令集 RV32I,常用的选项有:

- ① -march=rv32i, 仅支持基础 32 位整数指令集(RV32I)。

- ② -march=rv32im, 支持 RV32I + 乘除法扩展。

- ③ -march=rv32imc, 支持 RV32I + 乘除法扩展 + 16 位压缩指令扩展。

- (2)-mabi 选项被用来告知 GCC 其应该生成的 ABI,对 32 位基础指令集,常用的选项有:

- ① -mabi=ilp32, C语言中的 int、long 和指针类型都是 32 位, 浮点参数 通过整数寄存器传递。

- ②-mabi=ilp32f,-mabi=ilp32d,浮点参数通过浮点寄存器传递。

出于实际考虑,本书只讨论标准扩展中的32位乘除法扩展和16位压缩指令扩展部分。前者对数值计算非常重要,后者则能大大提高代码密度。

# 3.5.1 乘除法扩展(M Extension)

如图 3-24 所示, RISC-V 中根据乘数和被乘数的类型(有符号数/无符号数)和结果的截取范围(高32位/低32位),分别定义了4条32位的乘法指令,其结果也是32位。

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器 <b>2</b> | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | 14 | 000 | 2 11     7       目标寄存器        | 6 | 0110011 | <u>0</u><br>MUL 符号数乘法,<br>──保留低32位  |

|----|----------------------|--------------------------------------|--------------------------------------|----|-----|-------------------------------|---|---------|-------------------------------------|

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器2         | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | 14 | 001 | 2 <u>11</u> <u>7</u><br>目标寄存器 | 6 | 0110011 | <u>0</u><br>MULH 符号数乘法,<br>──保留高32位 |

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器2         | <u>19</u> <u>15</u><br>源寄存器1         | 14 | 010 | 2     11     7       目标寄存器    | 6 | 0110011 |                                     |

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器 <b>2</b> | <u>19</u> <u>15</u><br>源寄存器1         | 14 | 011 | 目标寄存器                         | 6 | 0110011 |                                     |

图3-24 乘法指令

同样,根据除数和被除数的类型(符号数/无符号数),RISC-V中定义了4条32位除法和余数指令,如图3-25所示。

| 31 | <u>25</u>            | <u>24</u> <u>20</u><br>源寄存器 <b>2</b> | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | <u>14</u> | 100 | <u>12</u> | 11     7       目标寄存器        | <u>6</u> | 0110011 | <u>0</u> | DIV<br>符号数除法的商    |

|----|----------------------|--------------------------------------|--------------------------------------|-----------|-----|-----------|-----------------------------|----------|---------|----------|-------------------|

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器2         | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | <u>14</u> | 101 | <u>12</u> | <u>11</u> <u>7</u><br>目标寄存器 | <u>6</u> | 0110011 | 0        | DIVU<br>无符号数除法的商  |

| 31 | <u>25</u>            | <u>24</u> <u>20</u><br>源寄存器2         | 19 15<br>源寄存器1                       | <u>14</u> | 110 | <u>12</u> | <u>11</u> <u>7</u><br>目标寄存器 | <u>6</u> | 0110011 | 0        | REM<br>符号数除法的余数   |

| 31 | <u>25</u><br>0000001 | <u>24</u> <u>20</u><br>源寄存器2         | <u>19</u> <u>15</u><br>源寄存器 <b>1</b> | <u>14</u> | 111 | <u>12</u> | <u>11</u> <u>7</u><br>目标寄存器 | <u>6</u> | 0110011 | 0        | REMU<br>无符号数除法的余数 |

图3-25 除法和余数指令

RISC-V 舍弃了条件编码和状态标志位,而采用有条件跳转指令来帮助判断溢出等状态,除法指令也沿袭了这一设计思路。在 RISC-V 的除法中,无论被除数和除数的值是什么,都不会让硬件产生异常。不过,下面两种情况是需要特别判断的。

# (1)除数为零。

在这种情况下, 商应为32位全1(32'hFFFFFFFF), 而余数应等于被除数。

# (2)符号数除法溢出。

这种情况只会发生在被除数为 $-2^{31}$ 而除数为-1的情况。由于补码(Two's Complement)中正数和负数的不对称性, $2^{31}$ 无法用32位符号数表示,导致溢出。在这种情况下,商应为32'h80000000,而余数则为0。

对 FPGA 实现来说,由于大部分的 FPGA 器件中都带有硬件乘法器,乘法指令可以直接用硬件乘法器来实现。而对除法和余数指令,既可以采用传统的移位相减的办法,又可以采用 SRT (Sweeney Robertson and Tocher)除法等实现快速除法。

# 3.5.2 压缩指令集扩展

为了提高代码密度, RISC-V 中引入了 16 位的压缩指令扩展(C Extension)。和 32 位指令集 RV32I 相比, C Extension的引入可以将代码密度提高 40% 左右。

RISC-V 的 C Extension 对 32 位、64 位和 128 位的指令集都做了扩展,所以被统称为 RVC。本书将只讨论其中对 32 位指令集的扩展部分,即 RV32C,并且讨论也将集中于整数指令集部分。

#### 1. C Extension 的格式

和许多 RISC 指令集不同, RISC-V 的 16 位压缩指令只是一个扩展(Extension), 而不是一个独立的指令集。在 RV32C 中的每一条指令,实际上都可以被转化为一条完整的 32 位指令。RV32C 只是对部分 32 位指令的一种简写方式,从而将纯 32 位代码转化为 16 位和 32 位的混合方式。这样做的好处是处理器如果需要支持 C Extension,只需要修改指令取指器和指令解码器就可以了,大大简化了处理器的设计。

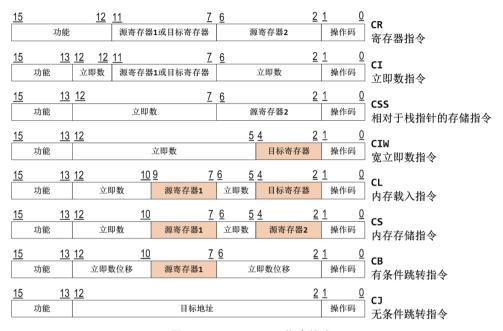

C Extension 中总共定义了 8 种指令格式,如图 3-26 所示。作为一种压缩指令扩展,C Extension 的指令格式中对立即数和寄存器都做了一些限制。

图3-26 C Extension指令格式

- (1) 立即数的位数被缩减。

- (2)寄存器的寻址有3位和5位两种方式。对3位的寄存器寻址(图3-26中深色标记部分),其仅限于部分通用寄存器( $x8\sim x15$ ,3'b000对应x8,3'b111对应x15)。由表3-1可以看到, $x8\sim x15$ 都是函数调用时必须用到的寄存器,临时寄存器没有被包含其中。

- (3)如果指令同时涉及源寄存器和目标寄存器,则二者必须相等(如图 3-26 中所示的 CB 格式,尽管在图 3-26 中只标注了源寄存器,但是实际上在某些具体的指令中,也包含源寄存器和目标寄存器相同的情形,图 3-32 和表 3-12 中采用的是 CB 格式的 C.ANDI 指令)。

# 2.16 位载入与存储压缩指令

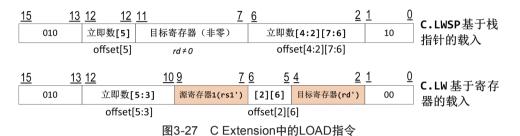

C Extension 中定义了两种 LOAD 指令,如图 3-27 所示。一种是基于栈指针(x2)

的 C.LWSP 指令,另一种是基于寄存器的 C.LW 指令。它们对应的 32 位指令可以 在表 3-7 中找到。

表 3-7 压缩 LOAD 指令对应的 32 位指令

| 16位压缩指令 | 对应的32位指令                             |

|---------|--------------------------------------|

| C.LWSP  | lw rd, offset[7:2](x2) $(rd \neq 0)$ |

| C.LW    | lw rd', offset[6:2](rs1')            |

图 3-27 中的立即数 (无符号数)都被左移 2 位,然后才被当作位移量。为此, 图 3-27 中的立即数都做了一些位的重新安排,其原因和衍生出 B-TYPE 和 J-TYPE 的原因是一样的,都是为了减小处理器实现的硬件开销,此处不再赘述。

另外,图 3-27 中的 C.LW 指令,其寄存器只有 3 位表示。为了和 5 位的寄存器加以区分,在其名称后加了单引号(rs1'与 rd',而不是 rs1与 rd)。

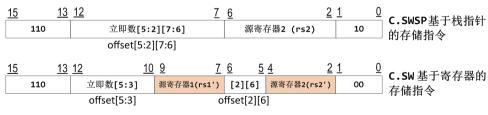

和 16 位载入压缩指令相类似, C Extension 中也分别基于栈指针(x2)和寄存器定义了两种存储指令,即 C.SWSP 和 C.SW。它们的定义如图 3-28 所示,对应的 32 位指令可以在表 3-8 中找到。由于 STORE 指令格式和前文的 LOAD 指令非常类似,这里就不再进一步展开。

图3-28 C Extension中的STORE指令

表 3-8 压缩 STORE 指令对应的 32 位指令

| 16位压缩指令 | 对应的32位指令                   |

|---------|----------------------------|

| C.SWSP  | sw rs2, offset[7:2](x2)    |

| C.SW    | sw rs2', offset[6:2](rs1') |

#### 3.16 位跳转压缩指令

C Extension 中定义了 4 条无条件跳转压缩指令, 其定义如图 3-29 所示,它们对应的 32 位指令可以在表 3-9 中找到。在这 4 条指令中, C.J 和 C.JR 都不会保存返回地址(默认目标寄存器为零),而 C.JAL 和 C.JALR 则默认目标寄存器为x1 (ra)。同时, C.JAL 和 C.JALR 的返回地址是 PC+2,而不是之前 32 位指令中的 PC+4。

| <u>15</u> | <u>13</u> <u>1</u> | <u>12</u> |                   |          |                    | <u>2</u> <u>1</u> |    | <u>0</u> |

|-----------|--------------------|-----------|-------------------|----------|--------------------|-------------------|----|----------|

|           | 101                | 立即        | 数(offset[11][4][9 | :8][1    | .0][6][7][3:1][5]) |                   | 01 | C.J      |

| <u>15</u> | <u>13</u> 1        | <u>12</u> |                   |          |                    | <u>2</u> <u>1</u> |    | <u>0</u> |

|           | 001                | 立即        | 数(offset[11][4][9 | :8][1    | .0][6][7][3:1][5]) |                   | 01 | C.JAL    |

| <u>15</u> |                    | <u>12</u> | <u>11</u>         | <u>7</u> | <u>6</u>           | <u>2</u> <u>1</u> |    | <u>0</u> |

|           | 1000               |           | 源寄存器1(rs1≠0)      |          | 源寄存器2(rs2)         |                   | 10 | C.JR     |

| <u>15</u> |                    | <u>12</u> | <u>11</u>         | <u>7</u> | <u>6</u>           | <u>2</u> <u>1</u> |    | <u>0</u> |

|           | 1001               |           | 源寄存器1(rs1≠0)      | )        | 源寄存器2(rs2)         |                   | 10 | C.JALR   |

图3-29 C Extension中的无条件跳转指令

表 3-9 无条件跳转压缩指令对应的 32 位指令

| 16位压缩指令 | 对应的32位指令             |

|---------|----------------------|

| C.J     | jal x0, offset[11:1] |

| C.JAL   | jal x1, offset[11:1] |

| C.JR    | jalr x0, rs1, 0      |

| C.JALR  | jalr x1, rs1, 0      |

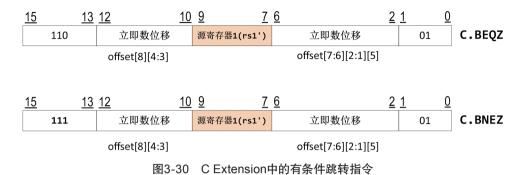

另外,C Extension 中还定义了 2 条有条件跳转压缩指令,其定义如图 3-30 所示,它们对应的 32 位指令可以在表 3-10 中找到。这两条指令都默认源寄存器 2 为 x0。

表 3-10 有条件跳转压缩指令对应的 32 位指令

| 16位压缩指令 | 对应的32位指令                  |

|---------|---------------------------|

| C.BEQZ  | beq rs1', x0, offset[8:1] |

| C.BNEZ  | bne rs1', x0, offset[8:1] |

# 4. 16 位整数计算压缩指令

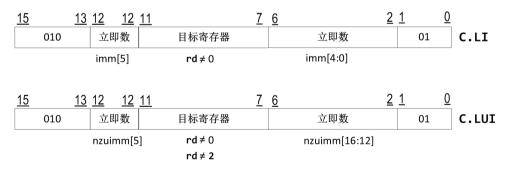

C Extension 中制定了 2 条压缩指令,来生成整数常量(Integer Constant-Generation Instruction)。它们的定义如图 3-31 所示,它们对应的 32 位指令可以在表 3-11 中找到。其中,C.LI 指令中的立即数需要做符号扩展,而 C.LUI 中的立即数则是非零的无符号数。

图3-31 C Extension中的常数生成指令

表 3-11 常数生成压缩指令对应的 32 位指令

| 7F 0    | 111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( 1111 ( ( 1111 ( ( 1111 ( ( ()))))))) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16位压缩指令 | 对应的32位指令                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C.LI    | addi rd, x0, imm[5∶0] (rd ≠ 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C.LUI   | lui rd, nzuimm[17:12] (rd $\neq$ 0,rd $\neq$ 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

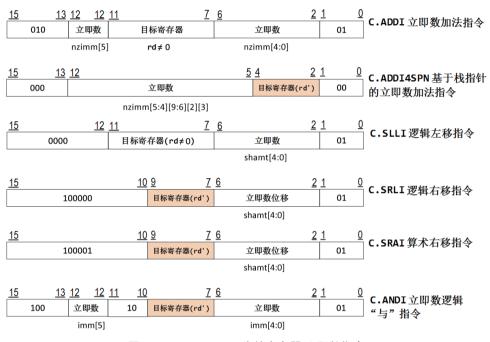

另外, C Extension 中还定义了 2 条立即数加法指令, 3 条立即数移位指令和 1 条立即数逻辑指令, 其定义如图 3-32 所示。它们对应的 32 位指令可以在表 3-12 中找到, 其中 C.ADDI4SPN 指令默认的源寄存器是 x2 (sp 栈指针), 以便基于栈指针的计算。

图3-32 C Extension中的寄存器-立即数指令

表 3-12 寄存器 - 立即数压缩指令对应的 32 位指令

| 27 - 313 AA - 13 |                                                 |

|------------------|-------------------------------------------------|

| 16位压缩指令          | 对应的32位指令                                        |

| C.ADDI           | addi rd, rd, nzimm[5∶0] (rd ≠ 0)                |

| C.ADDI4SPN       | addi rd', x2, nzuimm[9:2]                       |

| C.SLLI           | slli rd, rd, shamt[4:0] (shamt[4:0] $\neq$ 0)   |

| C.SRLI           | srli rd', rd', shamt[4:0] (shamt[4:0] $\neq$ 0) |

| C.SRAI           | srai rd', rd', shamt[4:0] (shamt[4:0] $\neq$ 0) |

| C.ANDI           | andi rd', rd', imm[5:0]                         |

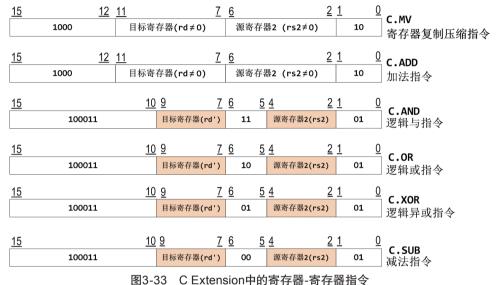

同时,和立即数指令相对应,C Extension中也定义了寄存器-寄存器操作的压缩指令,其定义如图 3-33 所示。它们对应的 32 位指令可以在表 3-13 中找到,其中的寄存器复制指令 C.MV 实际上是一条将源寄存器 1 默认为 x0 的加法指令。

图3-33 CEXICISION中的可行品-可行品指文

16位压缩指令

对应的32位指令

C.MV

add rd, x0, rs2

C.ADD

add rd, rd, rs2

C.AND

and rd', rd', rs2'

C.OR

or rd', rd', rs2'

C.XOR

xor rd', rd', rs2'

C.SUB

sub rd', rd', rs2'

表 3-13 寄存器 - 寄存器压缩指令对应的 32 位指令

# 5. 其他的 16 位压缩指令 (Miscellaneous)

# 1) C.NOP, 16 位空操作指令

和 32 位的空操作指令类似,C Extension 中也利用目标寄存器为零的加法指令来衍生出空操作指令,即  $c.nop = c.addi \ x0$ , $0 = addi \ x0$ ,x00

# 2) 16 位非法操作指令 (Illegal Instruction)

和 32 位指令集不同的是, C Extension 专门将全零的编码定义为非法操作指令, 以方便利用硬件异常来处理被零初始化的代码内存。

#### 3) 16 位软件断点指令(C.EBREAK)

C Extension 中也为 16 位压缩指令集定义了对应的软件断点指令, 其机器代码为 16'h9002。

# 6. 函数调用的开场白和收场白

在讨论函数调用约定时,曾经提到通用寄存器 x5 既可以作为临时寄存器(t0), 又可以作为替代链接寄存器(见表 3-1)。

之所以在 RISC-V 中引入 16 位压缩扩展指令集,其初衷就是为了降低代码量,提高代码密度。而在代码的每个函数调用的开始,往往都需要编写代码,将当前寄存器值保存到堆栈上。当函数返回时,也需要编写代码,将之前保存的寄存器值从堆栈恢复到寄存器。这两部分代码,分别称为开场白与收场白。由于函数的调用和返回在大部分代码中都会频繁出现,压缩指令集的设计者自然会希望将这部分代码的代码量降至最低。

由此,各种 RISC 指令集和处理器的设计者们给出了不同的解决方案。在加州大学伯克利分校设计的第一代 RISC 处理器(RISC I)和后来 SUN 公司的 SPARC 处理器当中,都采用了寄存器窗口的解决方案。但是寄存器窗口使得硬件开销变得非常大,而实际使用效果却并不理想,特别是当通用寄存器被耗尽时,其处理非常麻烦和缓慢,最终为后来的设计者所放弃。

后来的设计者如 ARM 公司,则在压缩指令集中引入了 Load-Multiple 和 Store-Multiple 指令。这些指令可以在一个指令周期内,将内存中多个地址连续的存储字载入多个寄存器,或反之将多个寄存器中的内容在一个指令周期内写入内存的连续地址。使用这些指令,自然可以极大降低开场白与收场白的代码量。根据 Andrew Waterman 在其博士论文中提供的统计数据,使用 Load-Multiple 和 Store-Multiple 以后,可以将 Linux 内核的代码量降低 8% 左右。

然而, RISC-V 的设计者再三斟酌后, 决定忍痛割爱, 不在 C Extension 中支持 Load-Multiple 与 Store-Multiple, 其原因主要如下:

- (1)在前文提到的所有 16 位压缩指令,都可以在 32 位指令集中找到对应的指令。也就是说,每一条 16 位压缩指令,都是其对应的 32 位指令的简写版。如果引入 Load-Multiple 与 Store-Multiple 指令,则会打破这一原则。

- (2)在3.3节中提到,RISC-V的设计目标之一就是希望指令集设计独立于具体的处理器实现。而引入Load-Multiple与Store-Multiple,会在一定程度上束缚处理器设计者的手脚,有违RISC-V的设计初衷。

- (3)对那些有 MMU(Memory Management Unit,内存管理单元)的处理器,会有虚拟地址(Virtual Address)和物理地址(Physical Address)两种不同的地址空间。程序在虚拟地址上运行,需要访问内存时,再通过 MMU 将虚拟地址转换为物理地址。这就导致在虚拟地址空间里连续的地址,转换为物理地址后可能不再连续。如果要在这种系统上实现 Load-Multiple 与 Store-Multiple,会大大增加硬件异常处理的难度。

因此, RISC-V 的设计者别出心裁, 在借鉴了 IBM S/390 计算机毫码程序之后, 提出了如下的方案:

- (1)由于开场白和收场白的工作仅仅只是将数据在堆栈和寄存器之间移动的,这些工作完全可以用共享的代码来实现。开场白和收场白本身也可以用类似函数调用的方式来实现。

- (2)然而,这种函数调用是一种特殊的函数调用,因为:

- ①这种调用本身不再需要开场白和收场白。

- ② 由于原先普通函数调用的返回地址需要使用 x1 (ra)来存放,调用开场白和收场白时则不能再使用 x1 (ra),而需要在函数调用约定中另外再分配一个寄存器。这个寄存器就是 x5 (t0/ 替代链接寄存器)。

- (3) 在软件实现时,可以做如下操作:

- ① 把原先的开场白代码,用 jal t0, shared\_prologue 代替,以调用共享的开场白代码,并将返回地址存入 x5 (t0)。

- ② 在共享的开场白代码中,用一连串的 c.swsp 指令将需要保存的寄存器值(其中也包括 x1(ra))推入堆栈中,最后用 c.jr t0 指令返回。

- ③ 把原先的收场白代码,用 jal x0, shared epilogue 代替。

- ④ 在共享的收场白代码中,用一连串的 c.lwsp 指令,将之前保存在堆栈上的寄存器值恢复到对应的寄存器中(其中也包括 x1(ra)),最后用 c.jr ra 结束整个函数调用。

根据 Andrew Waterman 提供的统计数据,使用以上类似毫码程序的方案以后,可以将 Linux 内核的代码量降低 7.5% 左右,其表现基本上和之前提到的 Load-Multiple/Store-Multiple 方案相当,但是却避免了 Load-Multiple/Store-Multiple 方案 带来的缺点。

# 3.6 RISC-V特权架构

如前所述,RISC-V的设计者将其官方标准分成了两部分:用户指令集与特权架构,其目的是希望不同特权架构的处理器可以在ABI互相兼容。换句话说,支持同一用户指令集的处理器可以根据实际需求而在特权架构的设计上采取不同的策略。

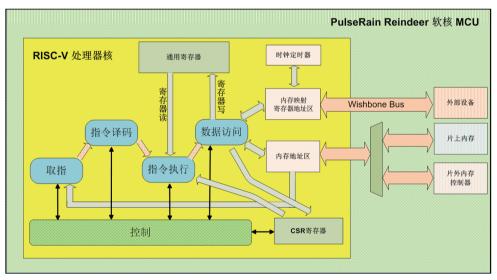

本书将在后文介绍的软核处理器属于 MCU (Microcontroller Unit, 微处理器单元)的范畴,本章将会重点讨论以下的内容:

- 特权层级,特别是机器模式(Machine Mode, M-Mode)。

- 控制状态寄存器。

- 机器层级指令集。

- 异常和中断。

- 调试。

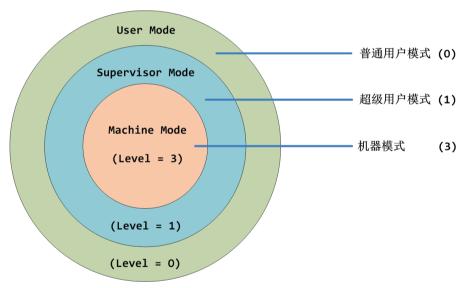

# 3.6.1 特权层级

RISC-V 处理器中的软件代码都是在硬件线程上运行的。为了加强对操作系统和信息安全的支持,RISC-V 替 HART 定义了 3 种工作模式(见图 3-34): 机器模式、超级用户模式(Supervisor Mode, S-Mode)和普通用户模式(User Mode, U-Mode)。每种模式分别对应一个特权层级(Privilege Levels)。其中机器模式的特权层级最高,而普通用户模式的特权层级最低。在高特权层级运行的代码比在低特权层级的代码拥有更多的权限,受到的约束也比低特权层级的代码要少。

图3-34 特权层级

在处理器设计时,机器模式是强迫要求实现的。其他的两个模式,处理器设计者则可以选择性地加以实现。一般来说,小规模的嵌入式系统只需要机器模式就可以了,而对信息安全有特殊要求的系统,则可能需要机器模式加普通用户模式。运行类似 UNIX 这样大型操作系统的处理器,则需要实现以上所有的模式。

UNIX 和信息安全不在本书的讨论范围之内,本书的剩余部分将会集中于机器模式的讨论。

# 3.6.2 控制状态寄存器

RISC-V 在特权架构部分单独定义了一个控制状态寄存器的地址空间,并分配了 12 位地址来做索引。在这 12 位地址当中,最高的两位 [11:10] 被用来指示寄存器的读写权限。如果这两位是 2'b11 的话,则表示该寄存器是只读寄存器;否则,该寄存器既可以被读取,又可以被写入。地址位 [9:8] 表示有权访问该寄存器的最低特权层级。对要讨论的机器模式 CSR,这两位都是 2'b11。在表 3-14 中列出了本书会涉及的所有 CSR 寄存器。

表 3-14 本书所涉及的 CSR 寄存器列表

| 地 址   | 读写权限 | 特权层级  | 寄存器名称     | 寄存器描述                    |

|-------|------|-------|-----------|--------------------------|

| 0xF11 | 只读   | 机器模式  | mvendorid | 厂商标识 (Vendor ID)         |

| 0xF12 | 只读   | 机器模式  | marchid   | 架构标识 (Architecture ID)   |

| 0xF13 | 只读   | 机器模式  | mimpid    | 实现标识 (Implementation ID) |

| 0xF14 | 只读   | 机器模式  | mhartid   | 硬件线程标识 (HART ID)         |

| 0x300 | 读写   | 机器模式  | mstatus   | 状态寄存器                    |

| 0x301 | 读写   | 机器模式  | misa      | 处理器所支持的指令集与扩展            |

| 0x304 | 读写   | 机器模式  | mie       | 中断允许                     |

| 0x305 | 读写   | 机器模式  | mtvec     | 异常相量寄存器,保存异常发            |

| 0x303 | 以与   | 化命快工  | mivec     | 生时的向量基准地址                |

| 0x340 | 读写   | 机器模式  | mscratch  | 草稿寄存器                    |

| 0x341 | 读写   | 机器模式  | mepc      | 保存异常发生时的程序寄存器值           |

| 0x342 | 读写   | 机器模式  | mcause    | 异常原因寄存器                  |

| 0x343 | 读写   | 机器模式  | mtval     | 参见后文有关异常处理的章节            |

| 0x344 | 读写   | 机器模式  | mip       | 待定的中断(参见后文有关中            |

| 0x344 | 以与   | 小品分类工 | ППР       | 断的章节)                    |

| 0xB00 | 读写   | 机器模式  | mcycle    | 机器周期计数器(低32位)            |

| 0xB02 | 读写   | 机器模式  | minstret  | 机器指令计数器(低32位)            |

| 0xB80 | 读写   | 机器模式  | mcycleh   | 机器周期计数器(高32位)            |

| 0xB82 | 读写   | 机器模式  | minstreth | 机器指令计数器(高 32 位)          |

表 3-14 看起来有点长,但这只是众多 CSR 寄存器中的一小部分。读者如果想了解 RISC-V 完整的 CSR 寄存器列表,则可以查找 RISC-V 的官方标准。本章就对表 3-14 中的寄存器做仔细讨论。

## 1. mvendorid 寄存器

为了对不同厂商设计生产的 RISC-V 处理器加以区分, RISC-V 在其特权架构标准部分制定了 mvendorid 寄存器, 用来存储厂商标识代码。对 RV32 来说, 这是一个 32 位的只读寄存器, 它的取值实际上是衍生于 JEDEC 厂商标识代码。

JEDEC 是联合电子设备工程委员会(Joint Electron Device Engineering Council)的 英文 缩写,目前的名称为 JEDEC 固态技术协会(Solid State Technology Association)。它是一个在1958年成立的行业协会组织,其总部位于美国弗吉尼亚州。所有的电子产品生产厂商都可以向 JEDEC 付费申请得到一个 JEDEC 的厂商标识代码(即 JEDEC 厂商标识代码)。

JEDEC 的厂商标识代码分为两部分:第一部分是 Bank 域 (Bank Field);第二部分是只有一字节的 Offset 域 (Offset Field)。对于这个 8 位的 Offset 域,其最高位是奇数校验码,其余 7 位对应 Bank 域里面的厂商标识。如果 Bank 域的值是 n, Offset 域的值是 m, 那么其对应的完整的 JEDEC 厂商标识代码应该是将 0x7F 重复 n-1 遍,然后再在后面接上 m。

例如 JEDEC 给美国 PulseRain Technology 公司分配厂商标识的文件中有如下文字:

the following JEDEC Manufacturer ID number has been assigned to your company:

94 decimal (bank 11)

0101 1110 binary

5E hex

由此,n=11,m=0x5E 其完整的 JEDEC 厂商标识代码就是:

由于 JEDEC 提供的厂商标识远超出了 32 位寄存器可以表示的范围,RISC-V 在特权架构标准中定义了一个方法,用来在 JEDEC 厂商标识代码的基础上衍生出一个 32 位的数值,然后固化于 mvendorid 寄存器中。根据 JEDEC 提供的 n 与 m 数值,RISC-V32 位厂商标识代码可以用如下公式产生:

Vendor ID=

$$((n-1) << 7) + (m & 0x7F)$$

(3-1)

根据上文 n=11,m=0x5E ,可以得出 PulseRain Technology 的 RISC-V 厂商标识代码为 0x55E。

# 2. marchid (体系架构标识代码)

根据 RISC-V 官方标准, marchid 在 RV32 下是一个 32 位的只读寄存器, 用来存放 HART 所对应的体系架构的标识代码。对于开源的架构来说,这个寄存器的值由 RISC-V 基金会负责在全球分配,其最高位必须是 0。对于商业公司所研发的架构来说,其值由具体的商业公司来分配,但是其最高位必须为 1,其余的位不能全为零。这样,如果将该寄存器和 mvendorid 寄存器一起使用,则可以唯一地标识HART 的体系架构。

如果处理器设计者选择不支持这个寄存器,则应该返回零值。

## 3. mimpid(实现标识代码)

根据 RISC-V 官方标准, mimpid 寄存器在 RV32 下也是一个 32 位的只读寄存器, 其主要的目的是标明处理器的版本号。该寄存器的格式完全由处理器设计者自行决定, 如果处理器设计者选择不支持该寄存器,则应该返回零值。

#### 4. mhartid (硬件线程标识)

在 RISC-V 的术语中,每个处理器核可以包含有多个硬件线程,称作 HART (Hardware Thread)。每个 HART 都有自己的程序计数器和寄存器空间,独立顺序运行指令。mhartid 寄存器用来给这些 HART 编号索引。在多处理器系统中,HART 的编号无须连续,但是必须至少有一个 HART 必须被编号为零。

#### 5. misa(指令集寄存器)

由于 RISC-V 指令集标准涵盖多种字长(32位/64位/128位), 并包含多种

指令集扩展(如 16 位压缩指令集扩展 C,乘除法扩展 M 等)。misa 寄存器的目的是为了向软件告知处理器具体支持的字长和扩展,以方便软件的可移植性。本寄存器各位完整的定义可以在 RISC-V 官方标准中找到。对于只支持单个 HART 和机器模式的 RV32 处理器来说,如表 3-15 所示的这些位值得关注。

位 索 引

注 释

[31:30]

MXL (Machine XLEN, 字长) (X Register Length, XLEN)

对 RV32 来说,这两位应该被置为 2'b01

[12]

M (乘除法扩展支持)

[8]

I (基础整数指令集支持)

该位总是为 1

[4]

E (RV32E 嵌入式指令集支持)

[3]

C (16 位压缩指令集支持)

表 3-15 指令集寄存器

# 6. mstatus (硬件线程状态寄存器)

mstatus 寄存器用来标识和控制 HART 的操作状态,其各位完整的定义可以在 RISC-V 官方标准中找到。对于只支持单个 HART 和机器模式的处理器来说,需要注意表 3-16 中的两个位。

| 位 索 引 | 注 释                                                 |  |  |  |  |  |  |

|-------|-----------------------------------------------------|--|--|--|--|--|--|

|       | mpie(machine previous interrupt enable,全局中断使能保持/恢复) |  |  |  |  |  |  |

| [7]   | 当中断或异常发生时,该位会记录下当前 mie 的值。当用 MRET 从中                |  |  |  |  |  |  |

|       | 断或异常中返回时,该位的值将被复制到 mie 中                            |  |  |  |  |  |  |

| [O]   | mie(machine interrupt enable,全局中断使能)                |  |  |  |  |  |  |

| [3]   | 当该位为零时,外部中断和时钟中断都将被禁止                               |  |  |  |  |  |  |

表 3-16 硬件线程状态寄存器

# 7. mscratch (草稿寄存器)

在 RV32 下,这是一个 32 位的读写寄存器。除了被用来作为 CSR 寄存器操作的读写测试以外,它还可以被操作系统作为暂存空间。

# 8. 与中断和异常有关的 CSR 寄存器

RISC-V 中还定义了多个 CSR 寄存器用来处理中断与异常, 其中与机器模式相关的部分主要如下:

- mtvec (machine trap vector base-address register, 机器模式异常向量基地址寄存器)。

- mip (machine interrupt register, pending interrupt, 机器模式中断等待寄存器)。

- mie (machine interrupt register, interrupt enable, 机器模式中断使能寄存器)。

- mcause (machine cause register, 机器模式异常原因寄存器)。

- mepc (machine exception program counter, 机器模式异常 PC 寄存器)。

- mtval (machine trap value register, 机器模式异常值寄存器)。

#### 9. 计数器

作为一种硬件性能监测的手段,RISC-V在其特权架构部分定义了一系列 计数器,用来记录从某一时间点开始后处理器已运行的时钟周期数和已执行的 指令数。具体来说,其主要包括如下的 CSR 寄存器。

#### 1) mcycle 与 mcycleh

RISC-V 中为机器模式定义了一个 64 位的 cycle 寄存器,用来记录机器已经运行的时钟周期数。这个寄存器的低 32 位和高 32 位分别存放在 mcycle 和 mcycleh 中。

对 RV32 来说,由于无法一次性地将 mcycle 和 mcycleh 同时读取出来,为了保证 64 位数据的完整性,需要在寄存器的读取方式上做一些处理。一种解法是要求软件总是先读取 mcycle,紧接着再读取 mcycleh。软件读取 mcycle 时,硬件同时将当时的 mcycleh 值保存下来,并在下次读取时提供该值。而另外一种解法则如代码 3-1 所示(参见 RISC-V 官方标准,将 cycle 寄存器的值读入到 x3:x2 中)。

# 代码3-1 64位cycle寄存器的读取

again:

rdcycleh x3

rdcycle x2

rdcycleh x4

bne x3, x4, again

# 2) minstret 与 minstreth

RISC-V 还为机器模式定义了一个 64 位的 instret 寄存器,用来记录机器已经完成的指令数(The Number of Instructions Retired)。该寄存器的低 32 位和高 32 位被分别存放在 minstret 与 minstreth 中。

同 cycle 寄存器一样,当在 RV32 中读取该寄存器时,也会面临保持 64 位数据 完整性的问题。其解法也与上述读取 cycle 寄存器的解法相同。

# 3.6.3 定时器

RISC-V 在设计时也对 RTC (Real Time Clock,实时时钟)的实现做了考虑。实际上,要在真正意义上实现一个实时时钟,需要以下几部分的硬件支持:

- (1)需要一个时钟定时器(Timer),运行在固定的频率。

- (2)需要能有办法获取时间基准,以用来计算实时时间(Wall Clock)。简单地说,就是要能有办法获取当前精确的日期与时间。在桌面系统中,这个时间基准可以通过网络从专门的时间服务器获取。在许多嵌入式系统里,这个时间基准可以通过 GPS 获取。

- (3)需要有办法能保持时钟定时器的不间断运行。这意味着 RTC 需要有自己的电源域,这样即使处理器的其他部分进入深度休眠状态,RTC 可以依然保持运行。而且 RTC 的电源域一般还需要有替代电源,如电池等。

为此, RISC-V 在其特权架构部分为机器模式定义了两个 64 位的寄存器: mtime 与 mtimecmp。同时, 为了方便 RTC 的独立运行, 减小实现 RTC 的硬件开销,

让多个 HART 能共享 RTC, RISC-V 中将这两个寄存器定义为内存映射寄存器(见图 3-4),以映射到内存空间中(而不是像 mcycle 这样定义为 CSR)。而这两个64 位寄存器在内存空间中的地址,则由具体的实现决定,RISC-V 标准中并没有对它们的地址做硬性规定。

#### 1. mtime 寄存器

mtime 是时钟定时器。一般来说,它应该以比较精确的石英晶体振荡器为时钟源,并以固定的频率做计数。然而,这个固定的频率具体是多少,RISC-V中并没有作出明确规定。许多系统将该频率设置为 32.768 kHz,因为 32.768 kHz 的晶振非常容易获得,而且 32.768 kHz 频率较低,适合做休眠时钟。另外,32 768 又是 2 的整数次幂,很容易由 32.768 kHz 产生周期为 1s 的时钟。

提示: 笔者在 RV32 的设计实践中发现,如果 mtime 的运行频率不能被处理器的主时钟频率整除的话,则可能会给软件,特别是嵌入式操作系统的运行带来额外的开销。因为操作系统在做任务调度时,需要对时间片有精确的计算。如果处理器的主时钟频率不是 mtime 运行频率的整数倍(如 mtime 运行于 32.768 kHz,而处理器主时钟频率为 100 MHz),则操作系统可能需要做非常复杂的 64 位除法运算。出于性能的考虑,这时操作系统往往要求处理器能支持硬件乘除法扩展(即支持 M Extension)。而对同样的嵌入式操作系统,如果处理器的主时钟频率是 mtime 运行频率的整数倍(如 mtime 运行于 1 MHz,而处理器主时钟频率为 100 MHz),则处理器只要支持基础整数指令集即可。

# 2. mtimecmp 寄存器

mtimecmp 的主要作用便是将其与 mtime 的值做比较。当 mtime 的值大于或等于 mtimecmp 时,便可触发产生时钟中断。

由于 mtimecmp 是一个 64 位的寄存器,在 RV32 系统中至少需要两条写指令才能完成对其的更新。而部分更新的 mtimecmp 寄存器值可能会误触发产生时钟中断。对此,通常的处理方法有两种:

- (1) 在更新 mtimecmp 之前禁止时钟中断 (Disable Timer Interrupt)。在 mtimecmp 更新完毕后再重置并允许时钟中断。

- (2) 采用 RISC-V 官方标准中建议的汇编代码序列(代码 3-2)。

假设需要写入 mtimecmp 的低 32 位存放于寄存器 a0 中, 而高 32 位存放于寄存器 a1 中, 如代码 3-2 所示。

# 代码3-2 mtimecmp的写入

注意:上面的汇编代码需要被完整并严格地顺序执行。编译器的优化,中断服务程序(Interrupt Service Routine, ISR)的插入,或者高端处理器的乱序执行都可能对上面代码的正确性产生影响。

# 3.6.4 中断与异常

#### 1. 中断与异常的比较

我们知道,软件并不总是按照其原先计划好的步骤运行,在多数情况下,软件 在执行过程中总会发生一些意外,使得处理器不得不暂停现有的软件执行步骤,转 而去做其他的额外处理。这种意外事件主要分为两种情况。

- (1)这种意外事件是由软件执行本身引发的。常见的情形包括:

- 软件在执行过程中访问了一个不存在的 CSR 寄存器。

- 软件在访问内存时没有按照字长对齐。

- 遭遇断点或者操作系统调用。

这种由软件本身引起的意外事件通常被称作异常(许多处理器会将被零除也作为一种异常,不过 RISC-V 的除法指令是不会产生异常的)。

(2)这种意外事件是由独立于软件运行的外部事件引发的。

这种由外部事件导致的意外通常被称作中断。在单个 HART 的机器模式下,中断主要来源于两个地方:

- ① 定时器中断。

- ②来自处理器核外部的中断,主要由外围设备产生。

在实际的硬件处理中,中断和异常的处理非常相近。

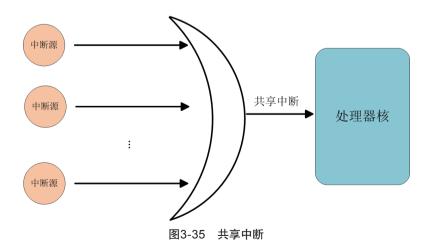

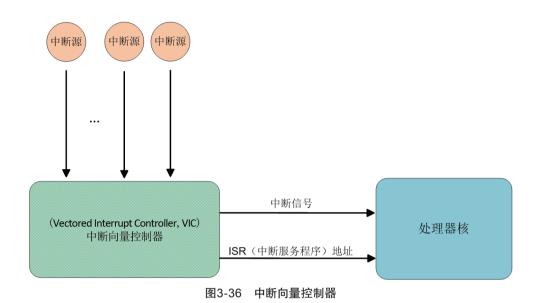

# 2. RISC-V 的中断控制器结构

在中小规模的嵌入式系统中,一般都会对中断信号的电气特性做直接处理。 具体地说,中断信号的电气特性一般有两种:电平触发(Level Trigger)和边沿触发(Edge Trigger),而且一般以电平触发居多。对于多个中断源的情况,可以简单地将它们线或(Wired-OR)在一起,作为共享中断,如图 3-35 所示。对于中断延迟要求比较高的情形,也可以用专门的中断向量控制器(Vectored Interrupt Controller,VIC)来处理,如图 3-36 所示。

在共享中断的情况下,处理器核在收到中断信号后,需要在中断处理程序中逐个查询外围设备,以确定中断源,因此其中断相应的延迟较大,其优点是硬件设计比较简单。对于像中断优先级、中断嵌套等问题,则大多都交由软件来处理。

为了减小中断延迟,许多中高端的嵌入式处理器都会在处理器核之外放置一个中断向量控制器,如图 3-36 所示。中断向量控制器在向处理器核提供中断信号的同时,还会提供与中断源相对应的 ISR(Interrupt Service Routine,中断服务程序)的入口地址。这些 ISR 的地址便组成了中断向量表(Interrupt Vector Table,IVT)。同时,中断向量控制器一般还会支持中断优先级、中断屏蔽等设置。与共享中断相比,中断向量控制器的硬件开销较大,但是软件处理则相对简单直接。

以上说的这两种方式都称为带外中断,其中断信号和数据是分开独立的。然而,随着系统规模的日益增大和高速串行数据传输的不断发展,点对点的拓扑结构变得流行起来。PCI-Express 总线便是其典型代表之一,它采用的中断机制被称为消息告知中断(Message Signaled Interrupt,MSI),这是一种带内中断的中断机制。在这种中断方式下,设备通过向某个指定的地址写入特殊的消息来发送中断信号。而外围设备也通过交换矩阵(Switch)和处理器核相连。MSI中断机制的优点是其可扩展性比较好,缺点是其软硬件都比较复杂。

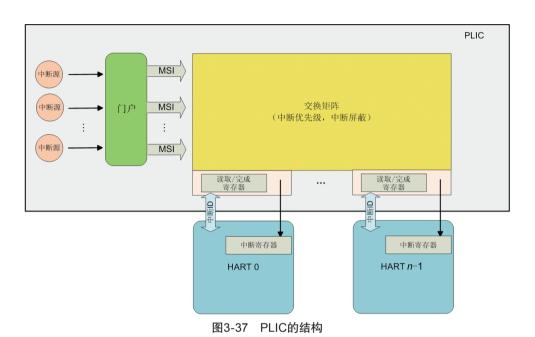

这种 MSI 中断机制和交换矩阵的思路显然也影响了 RISC-V 的设计者。在 RISC-V 标准中,对 RISC-V 的外部中断控制定义为 PLIC (Platform-Level Interrupt Controller,平台级中断控制器),其结构如图 3-37 所示。

从图 3-37 可以看出,PLIC 的设计考虑到了多个 HART 的情况。图 3-37 中门户的作用主要是将中断源来的中断电气信号转换为 MSI,然后交由交换矩阵来处理。交换矩阵可以被软件配置,以对中断优先级和中断屏蔽等做出设定。门户的另外一个作用是当来自某个中断源的中断正在被处理时,阻止接收同一中断源的后续中断。

对某个 HART 来说,如果中断发生,交换矩阵会通知 HART,而这种通知的方式可以有多种实现方式。对于复杂的系统,这种通知本身就可以是 MSI; 对于相对简单的系统,这种通知可以是简单的硬连线,直接连接到 HART 内部中断寄存器的等待中断位上。

HART 在收到来自交换矩阵的中断通知后,需要读取对应的读取 / 完成寄存器来确定中断源。读取 / 完成寄存器是一个内存映射寄存器,当其被读取时,会返回中断源的 ID (Indentifier)。同时,读取寄存器的动作也会被 PLIC 认定为对中断

的读取,从而修正 PLIC 中中断等待的状态。

当 HART 结束对中断的处理后,需要将刚才处理完成的中断源 ID 再写入读取 / 完成寄存器。PLIC 在收到这个写入动作后,会修改门户的状态,以允许接收对应中断源的后续中断。

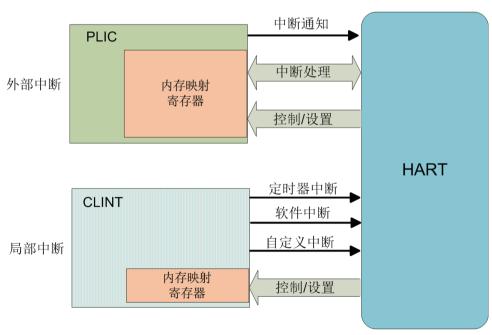

注意: 这里要提醒读者注意的是,PLIC 只包括对外部中断的处理。为方便RTC 的实现,RISC-V 标准中还专门定义了时钟定时器。而时钟定时器的中断属于局部中断 (Local Interrupt),其在 HART 中有专门的寄存器位对应。其他的局部中断还包括软件中断和处理器设计者的自定义局部中断。这些 Local Interrupt 会在后文讨论中断相关的寄存器时做详细讨论。在 SiFive 公司的Freedom E31 处理器中,将这些同局部中断相关的寄存器(时钟定时器寄存器、软件中断寄存器等)统称为核局部中断寄存器(Core Local Interruptor,CLINT)。所以对 HART 来说,其完整的中断拓扑结构如图 3-38 所示。

图3-38 外部中断和局部中断

这里笔者想借此机会对 PLIC/CLINT 的设计发表一些个人见解,供读者 参考:

- (1) RISC-V 的设计者对大规模的多处理器系统做了很多考量。从图 3-37 可以看出,RISC-V 的外部中断控制器有很好的可扩展性。然而,对于单个 HART 的仅支持机器模式的处理器核来说,这种结构显得比较复杂。同时和 图 3-36 相比,这种结构并不是纯粹的中断向量控制器结构。软件依然需要通过读取内存映射寄存器来确定中断源,而不是由硬件支持的中断向量表来直接调用 ISR。所以 PLIC 依然会有比较大的中断延迟。

- (2)在图 3-38 的架构下,如果需要进一步减少中断延迟,则可以通过CLINT中的自定义局部中断来实现。然而,在讨论相关的 CSR 寄存器时可以发现,RISC-V 对自定义局部中断的向量化处理并没有很完整的定义,向量编码可扩展的空间也非常有限,从而给 VIC 的实现造成了障碍。这就导致在目前的架构下,RISC-V 处理器的设计者不得不做一些额外的非标准设计来适应对中断延迟有严格要求的场合。

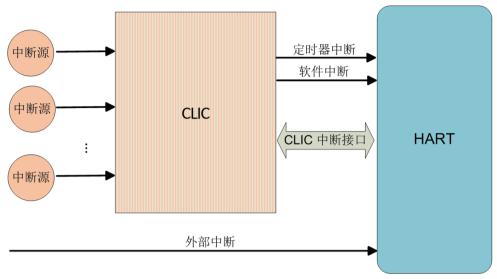

- (3)在本书撰写之际,RISC-V基金会发布的最新官方标准包括用户指令集 20190608 版和特权架构 20190608 版。上述对外部中断和局部中断的处理架构的讨论,都是基于这两个官方标准和之前的较早版本。然而,随着RISC-V在嵌入式系统中的应用和普及,RISC-V的设计者可能也意识到了目前中断处理架构的不足。所以 SiFive 公司又提议了一个新的中断处理的架构标准,叫作 CLIC(Core-Local Interrupt Controller,核局部中断控制器),并将其用在了 SiFive 公司的 E20 处理器上。CLIC 的结构如图 3-39 所示。

CLIC 可以被看作是 PLIC 和 CLINT 的合并与简化。图 3-39 的外部中断主要是用来在大规模系统与更高层级的 PLIC 相连的。实际上大部分的外设都可以直接被连接到 CLIC 上。同时 CLIC 架构标准中还定义了一些新的 CSR 寄存器,例如mtvt(machine trap vector table,机器模式异常向量表)等,用来加强对中断向量的支持。

图3-39 CLIC结构图

提示:在本书撰写之际,CLIC 架构标准还只是处在提议和草稿阶段。由于其目前还不是 RISC-V 的官方标准,本书在后续章节将不会对其再做进一步的深入讨论。有兴趣的读者可以在 GitHub 上找到更多的相关内容。

# 3. RISC-V 中断和异常的触发

在 RISC-V 中,对中断和异常的处理方式非常相近。二者一般都可以被称作异常情况。对于单个 HART 的机器模式,当异常情况发生时,硬件一般要经历以下的处理步骤:

# (1)确定中断是否被屏蔽。

对于单个 HART 的机器模式,下面两个 CSR 寄存器会影响中断的屏蔽。

- ① mstatus 寄存器中的 mie 位(见表 3-16),这是全局的中断使能位。但是该位不会屏蔽异常处理。

- ② mie ( machine interrupt register, interrupt enable, 机器模式中断使能寄存器)寄存器中的相关位。在 RV32 下, mie 寄存器是一个 32 位的可读写寄存器, 其与机器模式相关的位如表 3-17 所示。

表 3-17 mie 寄存器的位定义

| 位索引       | 注 释                |

|-----------|--------------------|

| 3         | 机器模式软件中断使能 (msie)  |

| 7         | 机器模式定时器中断使能 (mtie) |

| 11        | 机器模式外部中断使能 (meie)  |

| [31 : 12] | 供用户自定义扩展           |

这里对 RISC-V 特权架构中定义的软件中断做一下讨论。在 RISC-V 中,机器模式软件中断的主要目的是提供一种手段,用来在多 HART 系统中中断其他的 HART。为此,处理器的设计者需要在 CLINT 部分提供一个内存映射寄存器(或寄存器位),称为 msip(machine software interrupt pending,机器模式软件中断等待寄存器)。对 msip 的写操作会触发软件中断。

## (2)确定异常情况发生的原因。

当中断或异常发生时,处理器需要正确填写 CSR 寄存器 mcause 中的相关内容。对于 RV32 来说,机器模式异常原因寄存器 mcause 是一个 32 位的可读写寄存器(这意味着软件也可以修改其内容)。mcause 的 MSB,即位 31 被用来标识这个异常情况是中断还是异常。如果是中断,则该位应该被置为 1;如果是异常,则该位应被置为 0。mcause 剩下的位被用来作为异常编码。虽然在标准中称其为异常编码,但其也包括中断的情况(在中断情况下,异常编码实际上是中断源编号)。在目前的标准中,只用到了其中的低 4 位。对于单个 HART 的机器模式,如果异常情况是中断,则相关中断源编号如表 3-18 所示。如果异常情况是异常,则对应的异常种类编码如表 3-19 所示(细心的读者也许会发现,表 3-17 与表 3-18 的位定义是一样的)。

表 3-18 mcause 的中断源编号

| 异常编码 | 中断源编号     |

|------|-----------|

| 3    | 机器模式软件中断  |

| 7    | 机器模式定时器中断 |

| 11   | 机器模式外部中断  |

表 3-19 mcause 的异常种类编号

| 异常编码 | 异常种类         |  |  |  |

|------|--------------|--|--|--|

| 0    | 指令地址没有对齐     |  |  |  |

| 1    | 取指失败         |  |  |  |

| 2    | 非法指令         |  |  |  |

| 3    | 断点           |  |  |  |

| 4    | 内存数据读取地址没有对齐 |  |  |  |

| 5    | 内存数据读取失败     |  |  |  |

| 6    | 内存数据写入地址没有对齐 |  |  |  |

| 7    | 内存数据写入失败     |  |  |  |

| 11   | 机器模式下的环境调用   |  |  |  |

# (3)确定异常情况发生的地址。

对于机器模式, RISC-V 在其特权架构标准中定义了 mepc (machine exception program counter, 机器模式异常程序计数器)寄存器, 用来存放异常情况发生时的程序计数器的值。对于异常来说, 当前触发异常的指令的 PC 值是一个重要参数, 所以 mepc = PC。而对中断来说, mepc 值则会被中断处理程序末尾的 MRET (M-Return)指令用来作为中断返回地址。所以, mepc 需要存放下一条指令的地址。

## (4)确定与异常情况相关的参数。

为了帮助异常情况的处理,RISC-V还在其特权架构标准的机器模式中定义了mtval寄存器,以提供与异常情况相关的参数。在RV32下,mtval是一个32位的可读写寄存器。当内存访问出现异常时,对应的内存读写地址应该被保存在这个寄存器里。

(5)改变 PC 值,调用中断/异常处理程序,并设置相应的中断比特状态位。

对于机器模式, RISC-V 在其特权架构标准中定义了 mtvec 寄存器, 用来确定异常情况处理程序的地址, 在 RV32 下, 这是一个 32 位的可读写寄存器。其中的低两位用来确定中断模式, 其余高 30 位被用来作为基地址(BASE)。中断模式的定义如表 3-20 所示。

表 3-20 mtvec 的中断模式定义

|      | The second secon |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 中断模式 | 中断方式描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0    | 直接模式。在该模式下,新的 PC 值被直接设置为 mtvec 中的基地址值。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 即 PC = BASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |