# MIPS® Architecture For Programmers Volume II-A: The MIPS64® Instruction Set Reference Manual

Document Number: MD00087 Revision 6.06 December 15, 2016

Copyright © 2016 Imagination Technologies LTD. and/or its Affiliated Group Companies. All rights reserved.

# **Contents**

| Chapter 1: About This Book                                | 14 |

|-----------------------------------------------------------|----|

| 1.1: Typographical Conventions                            |    |

| 1.1.1: Italic Text                                        |    |

| 1.1.2: Bold Text                                          | 15 |

| 1.1.3: Courier Text                                       |    |

| 1.2: UNPREDICTABLE and UNDEFINED                          |    |

| 1.2.1: UNPREDICTABLE                                      |    |

| 1.2.2: UNDEFINED                                          |    |

| 1.2.3: UNSTABLE                                           |    |

| 1.3: Special Symbols in Pseudocode Notation               |    |

| 1.4: Notation for Register Field Accessibility            |    |

| 1.5: For More Information                                 |    |

| Chapter 2: Guide to the Instruction Set                   | 22 |

| 2.1: Understanding the Instruction Fields                 | 22 |

| 2.1.1: Instruction Fields                                 |    |

| 2.1.2: Instruction Descriptive Name and Mnemonic          | 24 |

| 2.1.3: Format Field                                       | 24 |

| 2.1.4: Purpose Field                                      | 25 |

| 2.1.5: Description Field                                  | 25 |

| 2.1.6: Restrictions Field                                 |    |

| 2.1.7: Availability and Compatibility Fields              | 26 |

| 2.1.8: Operation Field                                    | 27 |

| 2.1.9: Exceptions Field                                   |    |

| 2.1.10: Programming Notes and Implementation Notes Fields |    |

| 2.2: Operation Section Notation and Functions             |    |

| 2.2.1: Instruction Execution Ordering                     |    |

| 2.2.2: Pseudocode Functions                               |    |

| 2.3: Op and Function Subfield Notation                    |    |

| 2.4: FPU Instructions                                     | 40 |

| Chapter 3: The MIPS64® Instruction Set                    |    |

| 3.1: Compliance and Subsetting                            |    |

| 3.1.1: Subsetting of Non-Privileged Architecture          |    |

| 3.2: Alphabetical List of Instructions                    |    |

| ABS.fmt                                                   |    |

| ADD.                                                      |    |

| ADD.fmt                                                   |    |

| ADDI                                                      |    |

| ADDIU                                                     |    |

| ADDIUPC                                                   |    |

| ADDU                                                      |    |

| ALIGN DALIGN                                              |    |

| ALNV.PS                                                   |    |

| ALUIPC                                                    |    |

| AND                                                       |    |

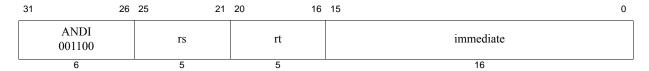

| ANDI                                                      | 58 |

| AUI DAUI DAHI DATI                 |     |

|------------------------------------|-----|

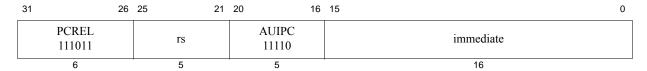

| AUIPC                              | 62  |

| B                                  |     |

| BAL                                | 64  |

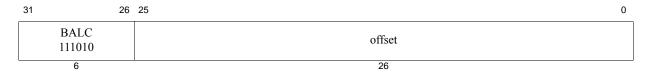

| BALC                               | 66  |

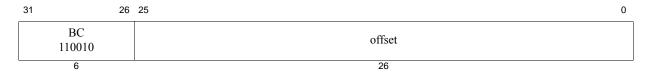

| BC                                 | 67  |

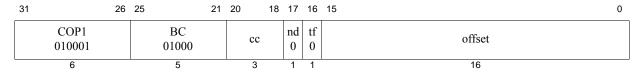

| BC1EQZ BC1NEZ                      |     |

| BC1F                               |     |

| BC1FL                              |     |

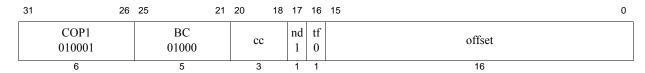

| BC1T                               |     |

| BC1TL                              |     |

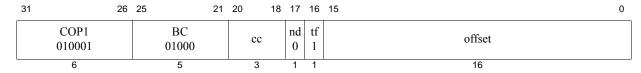

| BC2EQZ BC2NEZ                      |     |

| BC2F                               |     |

| BC2FL                              |     |

|                                    |     |

| BC2T                               |     |

| BC2TL                              |     |

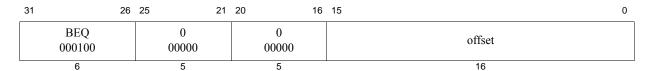

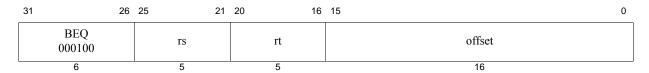

| BEQ                                |     |

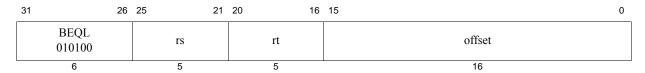

| BEQL                               |     |

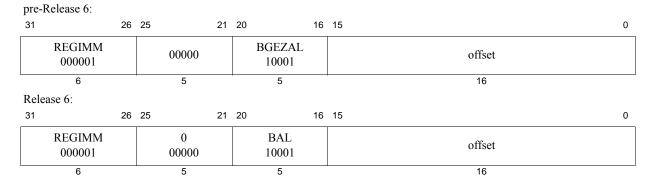

| BGEZ                               |     |

| BGEZAL                             |     |

| B{LE,GE,GT,LT,EQ,NE}ZALC           | 91  |

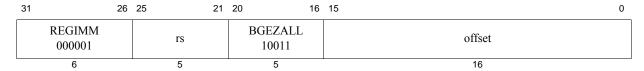

| BĞEZALL                            | 94  |

| B <cond>C</cond>                   | 96  |

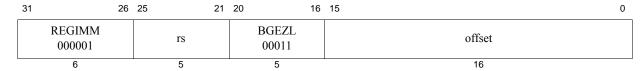

| BGEZL                              | 100 |

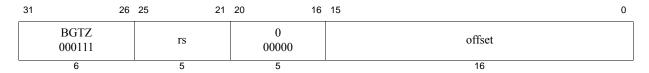

| BGTZ                               |     |

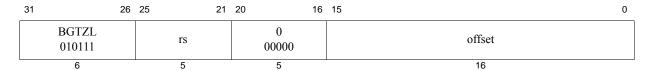

| BGTZL                              |     |

| BITSWAP DBITSWAP                   |     |

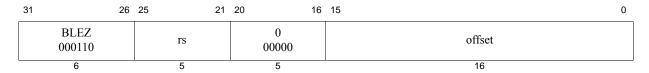

| BLEZ                               |     |

| BLEZL                              |     |

| BLTZ                               |     |

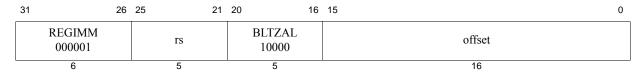

| BLTZAL                             |     |

|                                    |     |

| BLTZALL                            |     |

| BLTZL                              |     |

| BNE                                |     |

| BNEL                               |     |

| BOVC BNVC                          |     |

| BREAK                              | 121 |

| C.cond.fmt                         | 122 |

| CACHE                              | 126 |

| CACHEE                             | 133 |

| CEIL.L.fmt                         | 139 |

| CEIL.W.fmt                         | 140 |

| CFC1                               |     |

| CFC2                               |     |

| CLASS.fmt                          |     |

| CLO                                |     |

| CLZ                                |     |

| CMP.condn.fmt                      |     |

|                                    |     |

| COP2                               |     |

| CRC32B, CRC32H, CRC32W, CRC32D     |     |

| CRC32CB, CRC32CH, CRC32CW, CRC32CD |     |

| CTC1                               |     |

| OTOD                               | 164 |

| CVT.D.fmt                               | 165 |

|-----------------------------------------|-----|

| CVT.L.fmt                               | 166 |

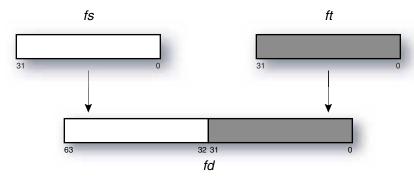

| CVT.PS.S                                | 167 |

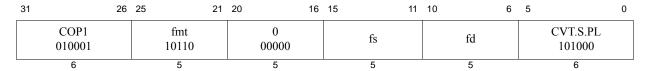

| CVT.S.PL                                | 169 |

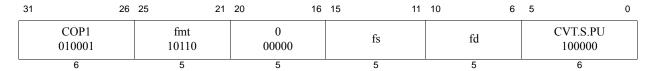

| CVT.S.PU                                | 170 |

| CVT.S.fmt                               |     |

| CVT.W.fmt                               |     |

| DADD                                    |     |

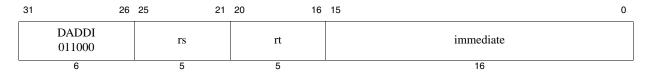

| DADDI                                   |     |

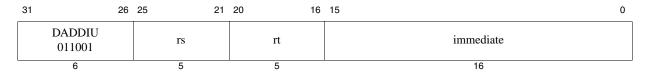

| DADDIU                                  |     |

|                                         |     |

| DADDU                                   |     |

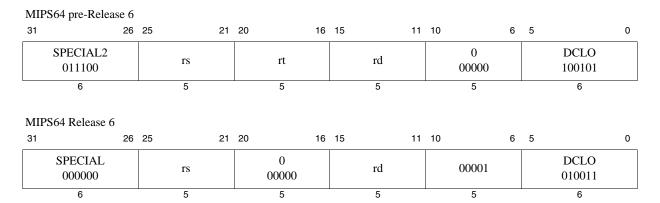

| DCLO                                    |     |

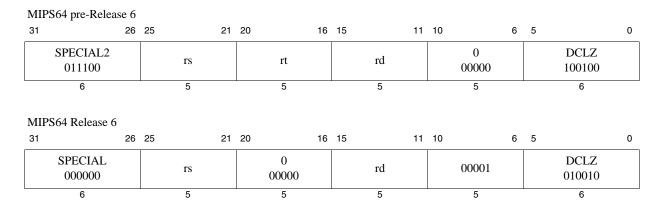

| DCLZ                                    |     |

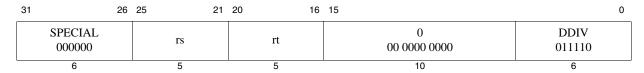

| DDIV                                    |     |

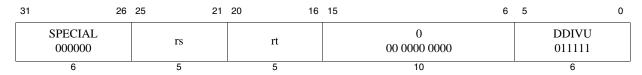

| DDIVU                                   |     |

| DERET                                   | 181 |

| DEXT                                    | 182 |

| DEXTM                                   | 184 |

| DEXTU                                   | 186 |

| DI                                      | 188 |

| DINS                                    |     |

| DINSM                                   |     |

| DINSU                                   |     |

| DIV                                     |     |

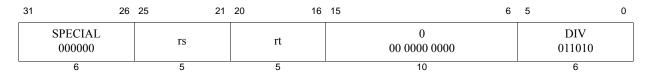

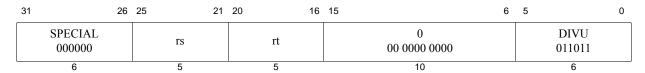

| DIV MOD DIVU MODU DDIV DMOD DDIVU DMODU |     |

|                                         |     |

| DIV.fmt                                 |     |

| DIVU                                    |     |

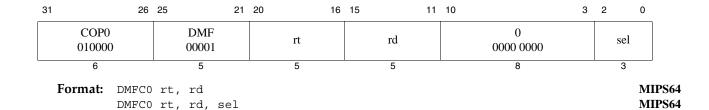

| DMFC0                                   |     |

| DMFC1                                   |     |

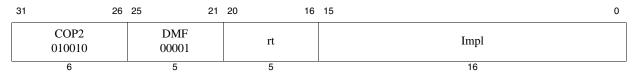

| DMFC2                                   |     |

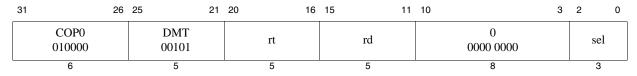

| DMTC0                                   | 205 |

| DMTC1                                   | 206 |

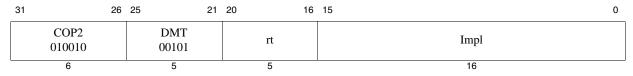

| DMTC2                                   | 207 |

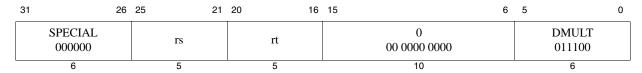

| DMULT                                   | 208 |

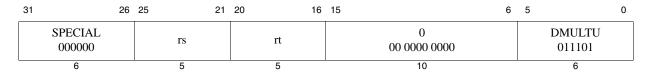

| DMULTU                                  | 209 |

| DROTR                                   | 210 |

| DROTR32                                 |     |

|                                         | 212 |

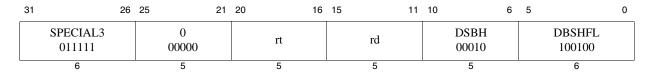

| DSBH                                    |     |

| DSHD                                    |     |

| DSLL                                    |     |

|                                         |     |

| DSLL32                                  |     |

| DSLLV                                   |     |

| DSRA                                    |     |

| DSRA32                                  |     |

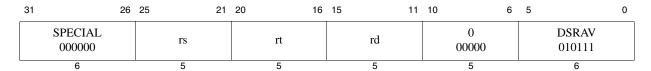

| DSRAV                                   |     |

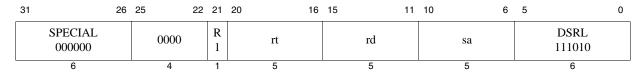

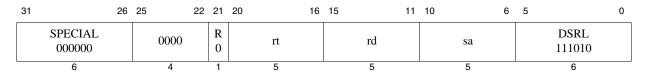

| DSRL                                    | 221 |

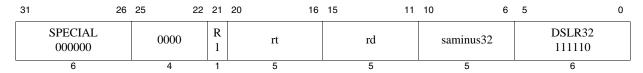

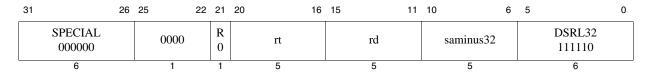

| DSRL32                                  | 222 |

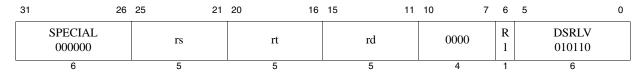

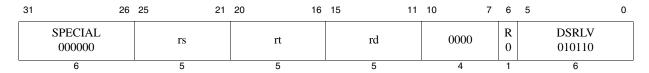

| DSRLV                                   | 223 |

| DSUB                                    |     |

| DSUBU                                   |     |

| DVP                                     |     |

| EHB                                     |     |

| בו וב                                   |     |

| El          | 230        |

|-------------|------------|

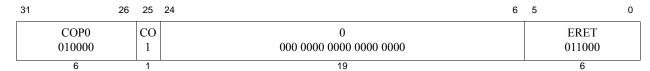

| ERET        | 231        |

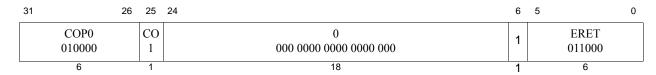

| ERETNC      | 233        |

| EVP         | 235        |

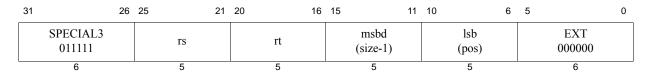

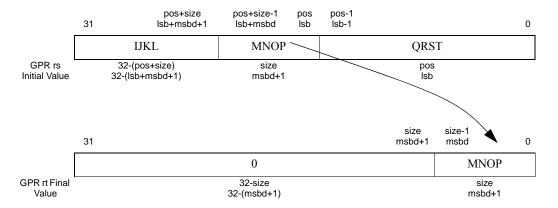

| EXT         | 237        |

| FLOOR.L.fmt | 239        |

| FLOOR.W.fmt | 240        |

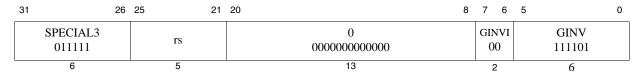

| GINVI       | 241        |

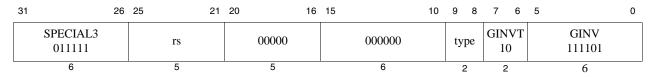

| GINVT       | 243        |

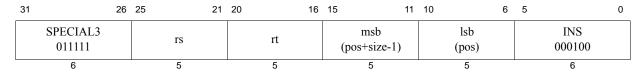

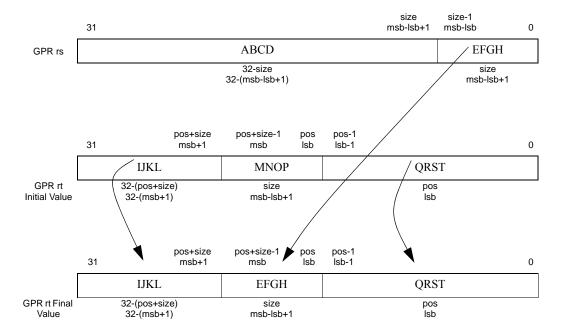

| NS          | 246        |

|             | 248        |

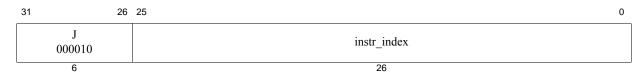

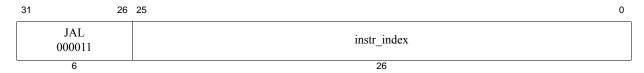

| JAL         | 249        |

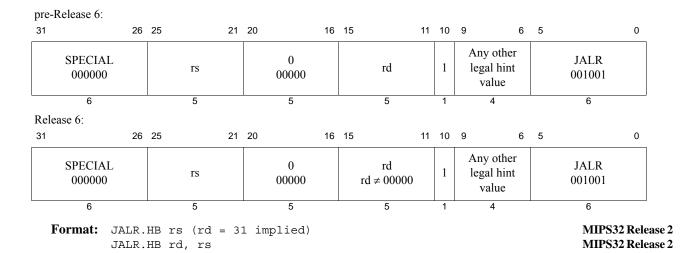

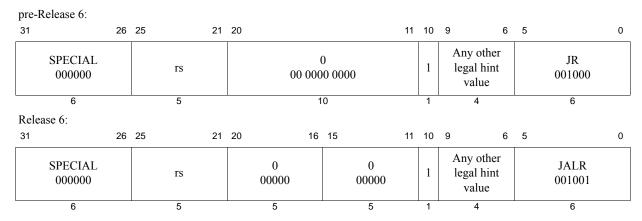

| JALR        |            |

| JALR.HB.    |            |

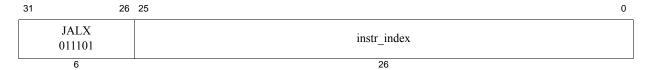

| JALX        |            |

| JIALC       |            |

| JIC         |            |

| JR          |            |

| JR.HB.      |            |

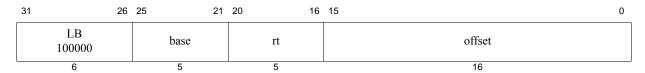

| LB          |            |

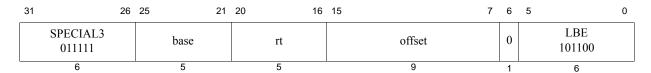

| LBE         |            |

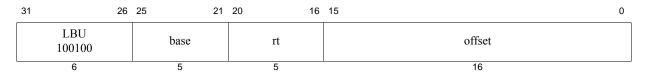

| LBU         |            |

|             |            |

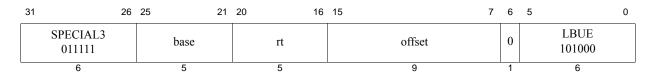

| LBUE        |            |

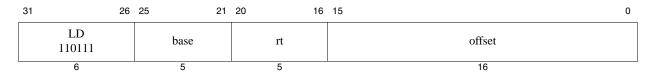

| LD          |            |

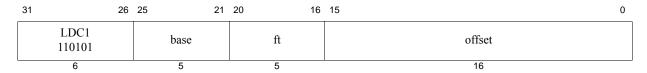

| LDC1        | _          |

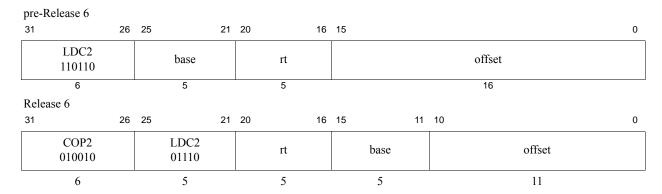

| LDC2        |            |

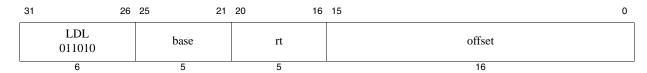

| LDL         | _          |

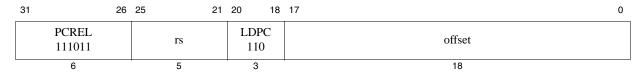

| LDPC        |            |

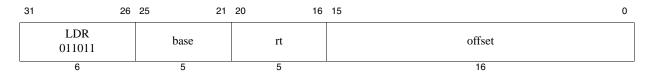

| LDR         |            |

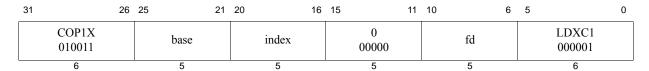

| LDXC1       | _          |

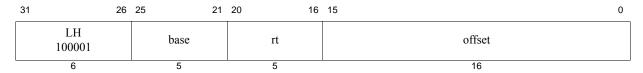

| LH          |            |

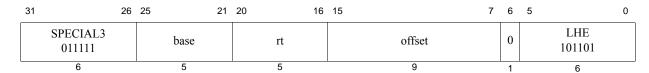

| LHE         |            |

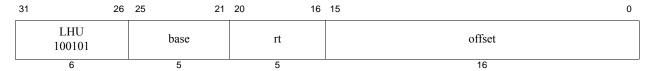

| LHU         |            |

| LHUE        |            |

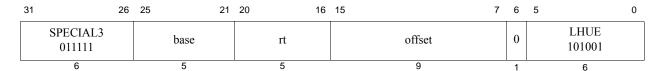

| Ц           |            |

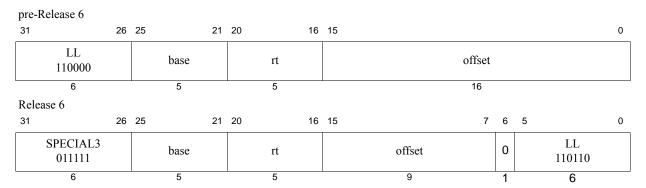

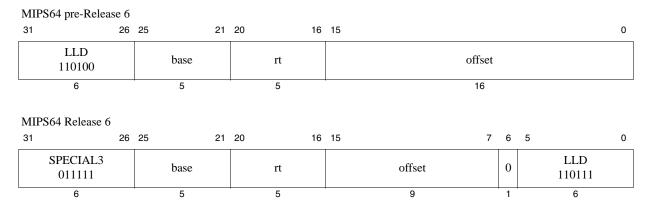

| LLD         |            |

| LE          | 287        |

| LLDP        | 289        |

| LLWP        | 291        |

| LLWPE       | 293        |

| LSA DLSA    | 295        |

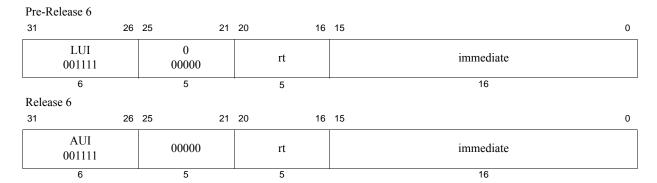

| LUI         | 296        |

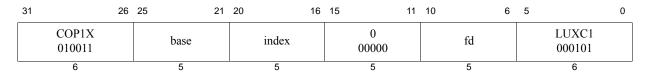

| LUXC1       | 297        |

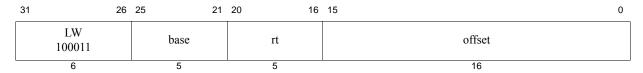

| LW          | 298        |

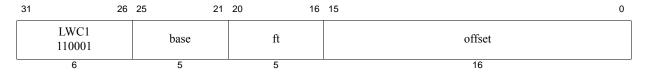

| LWC1        | 299        |

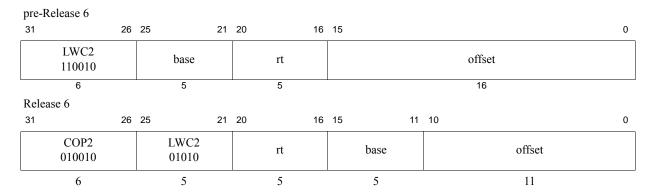

| LWC2        |            |

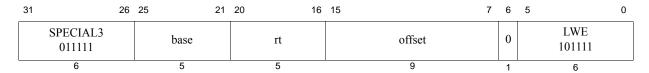

| LWE         |            |

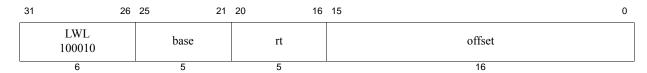

| LWL         |            |

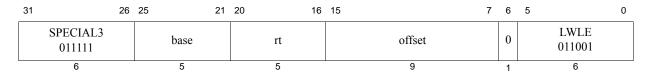

| LWLE        |            |

| LWPC        |            |

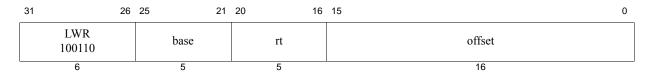

| LWR         |            |

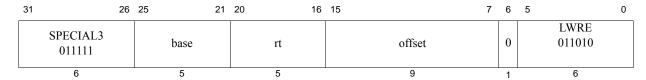

| LWRE        |            |

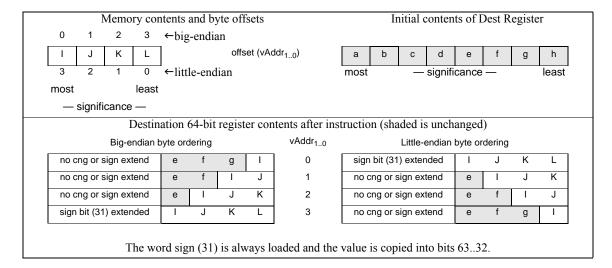

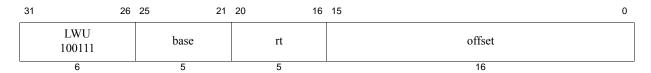

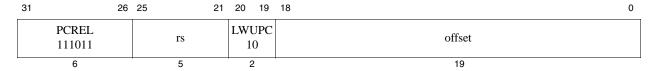

| WHI         | 314<br>318 |

| LWUPC                              | 319 |

|------------------------------------|-----|

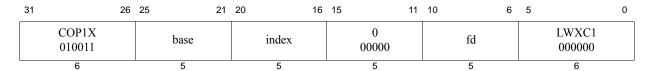

| LWXC1                              | 320 |

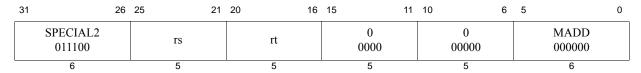

| MADD                               | 321 |

| MADD.fmt                           | 322 |

| MADDF.fmt MSUBF.fmt                | 324 |

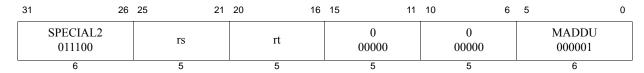

| MADDU                              | 326 |

| MAX.fmt MIN.fmt MAXA.fmt MINA.fmt  | 327 |

| MFC0                               |     |

| MFC1                               |     |

| MFC2                               |     |

| MFHC0                              |     |

| MFHC1                              |     |

| MFHC2                              |     |

| MFHI                               |     |

|                                    |     |

| MFLO                               |     |

| MOV.fmt                            |     |

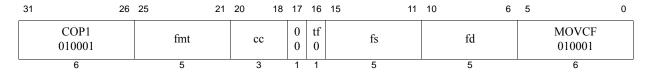

| MOVF                               |     |

| MOVF.fmt                           |     |

| MOVN                               |     |

| MOVN.fmt                           |     |

| MOVT                               | 346 |

| MOVT.fmt                           | 347 |

| MOVZ                               | 349 |

| MOVZ.fmt                           | 350 |

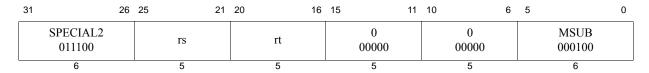

| MSUB                               | 351 |

| MSUB.fmt                           | 352 |

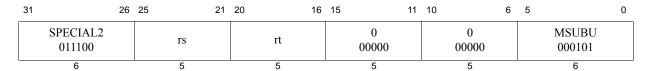

| MSUBU                              | 354 |

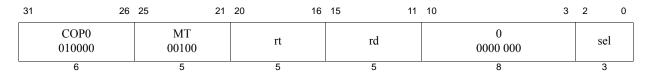

| MTC0                               | 355 |

| MTC1                               |     |

| MTC2                               |     |

| MTHC0                              |     |

| MTHC1                              |     |

| MTHC2                              |     |

| MTHI.                              |     |

| MTLO                               |     |

|                                    |     |

|                                    |     |

| MUL MOR MORO MORO DMOR DMORO DMORO | 367 |

|                                    | 370 |

| MULT                               |     |

| MULTU                              |     |

| NAL                                |     |

| NEG.fmt                            |     |

| NMADD.fmt                          |     |

| NMSUB.fmt                          |     |

| NOP                                |     |

| NOR                                | 381 |

| OR                                 | 382 |

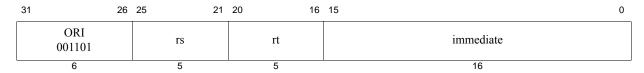

| ORI                                | 383 |

| PAUSE                              | 385 |

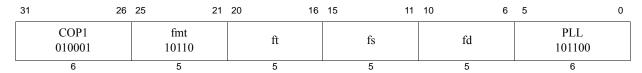

| PLL.PS                             |     |

| PLU.PS.                            |     |

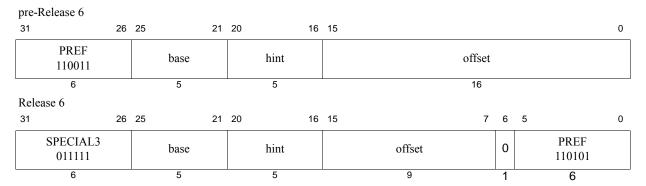

| PREF                               |     |

|                                    | 393 |

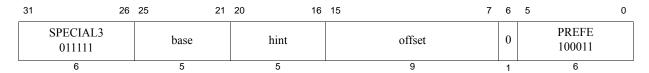

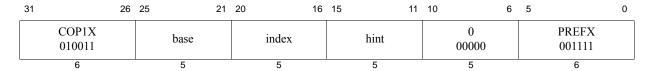

| PREFX                  | 397 |

|------------------------|-----|

| PUL.PS                 | 398 |

| PUU.PS                 | 399 |

| RDHWR                  | 400 |

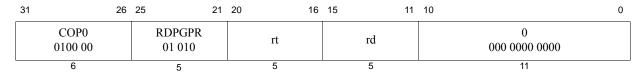

| RDPGPR                 | 403 |

| RECIP.fmt              | 404 |

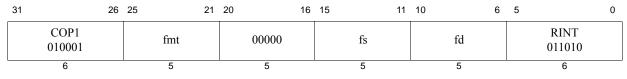

| RINT.fmt               |     |

| ROTR                   |     |

| ROTRV                  |     |

| ROUND.L.fmt            |     |

| ROUND.W.fmt            |     |

| RSQRT.fmt              |     |

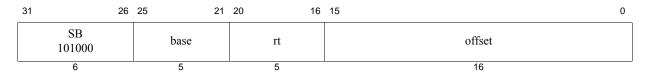

| SB.                    |     |

|                        |     |

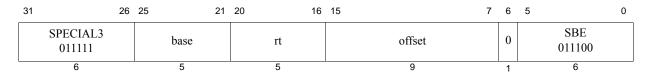

| SBE                    |     |

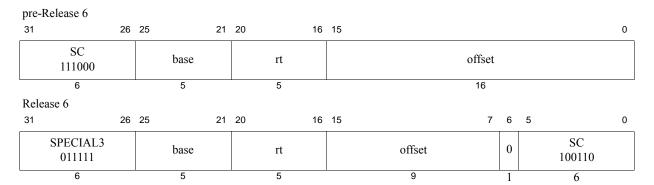

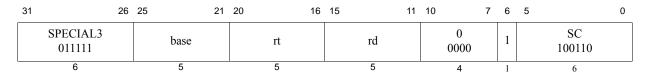

| SC                     |     |

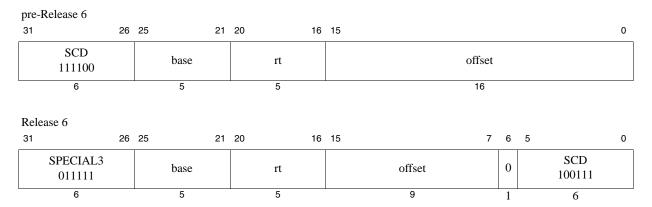

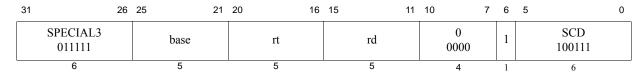

| SCD                    |     |

| SCDP                   |     |

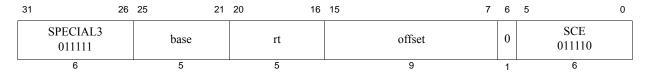

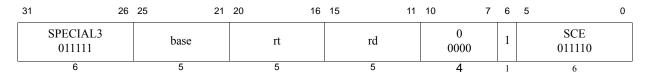

| SCE                    |     |

| SCWP                   | 428 |

| SCWPE                  | 432 |

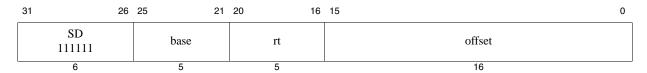

| SD                     | 435 |

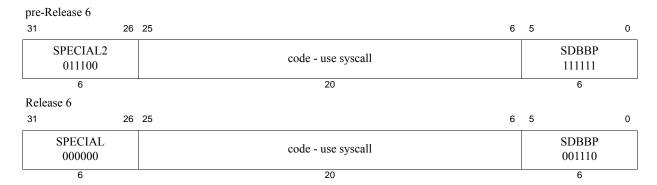

| SDBBP                  | 436 |

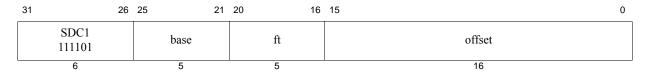

| SDC1                   |     |

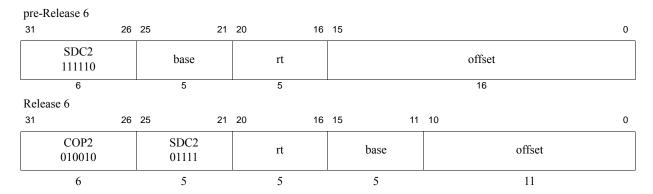

| SDC2                   |     |

| SDL                    |     |

| SDR                    |     |

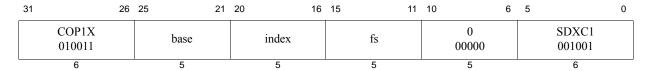

| SDXC1                  |     |

| SEB                    |     |

| SEH.                   |     |

|                        |     |

| SEL.fmt                |     |

| SELEQZ SELNEZ          |     |

| SELEQZ.fmt SELNEQZ.fmt |     |

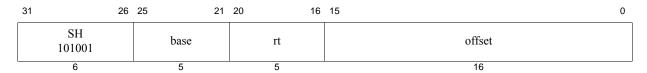

| SH                     |     |

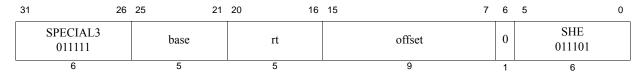

| SHE                    |     |

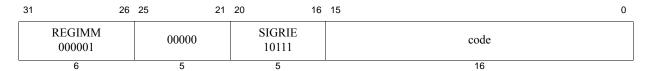

| SIGRIE                 | 457 |

| SLL                    | 458 |

| SLLV                   | 459 |

| SLT                    | 460 |

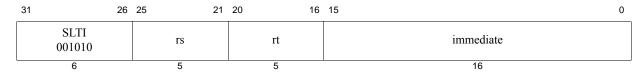

| SLTI                   | 461 |

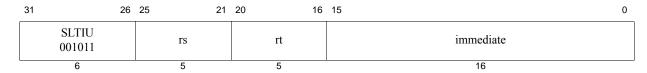

| SLTIU                  |     |

| SLTU                   |     |

| SQRT.fmt               |     |

| SRA                    |     |

| SRAV                   |     |

|                        |     |

| SRL                    |     |

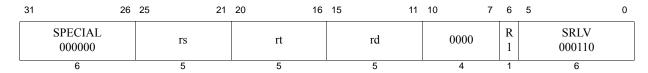

| SRLV                   |     |

| SSNOP                  |     |

| SUB                    |     |

| SUB.fmt                |     |

| SUBU                   | 472 |

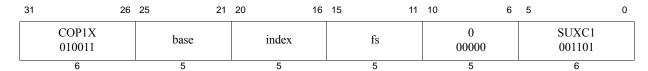

| SUXC1                  | 473 |

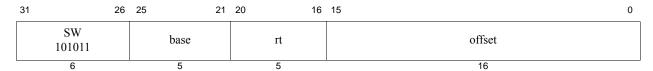

| SW                     | 474 |

| RWC1                   | 475 |

| Appendix B: Revision History                       | 549 |

|----------------------------------------------------|-----|

| A.T. Holoase o matruction Encountys                |     |

| A.4: Release 6 Instruction Encodings               |     |

| A.2: Instruction Bit Encoding Tables               |     |

| A.1: Instruction Encodings and Instruction Classes |     |

| Appendix A: Instruction Bit Encodings              |     |

| A PARA PROPERTY                                    |     |

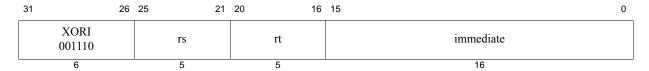

| XORI                                               | 529 |

| XOR                                                |     |

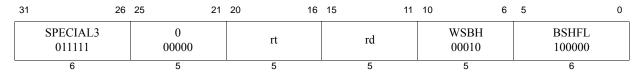

| WSBH                                               |     |

| WRPGPR                                             |     |

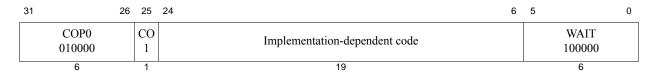

| WAIT                                               |     |

| TRUNC.W.fmt                                        |     |

| TRUNC.L.fmt                                        |     |

| TNEI                                               |     |

| TNE                                                |     |

| TLTU                                               | 519 |

| TLTIU                                              | 518 |

| TLTI                                               | 517 |

| TLT                                                |     |

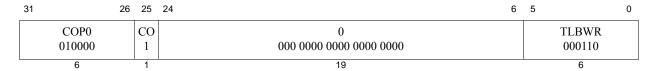

| TLBWR                                              | 514 |

| TLBWI                                              |     |

| TLBR                                               |     |

| TLBP                                               |     |

| TLBINVF                                            |     |

| TLBINV                                             |     |

| TGEU                                               |     |

| TGEIU                                              |     |

| TGETGEI                                            |     |

| TEQI                                               |     |

| TEQ                                                |     |

| SYSCALL                                            |     |

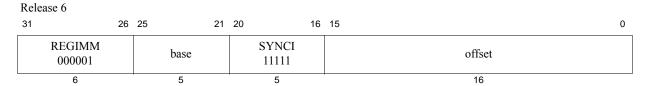

| SYNCI                                              |     |

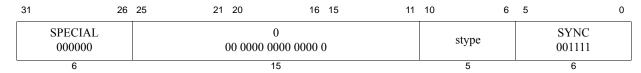

| SYNC                                               |     |

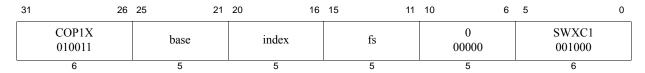

| SWXC1                                              |     |

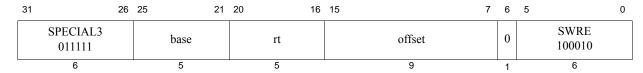

| SWRE                                               |     |

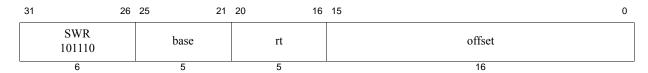

| SWR                                                |     |

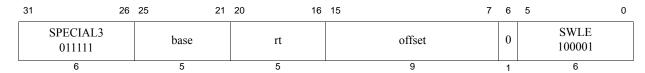

| SWLE                                               |     |

| SWL                                                | 478 |

| SWE                                                | 477 |

| SWC2                                               | 476 |

# **List of Figures**

| Figure 2.1: Example of Instruction Description                      | 23  |

|---------------------------------------------------------------------|-----|

| Figure 2.2: Example of Instruction Fields                           | 24  |

| Figure 2.3: Example of Instruction Descriptive Name and Mnemonic    | 24  |

| Figure 2.4: Example of Instruction Format                           | 24  |

| Figure 2.5: Example of Instruction Purpose                          | 25  |

| Figure 2.6: Example of Instruction Description                      |     |

| Figure 2.7: Example of Instruction Restrictions                     | 26  |

| Figure 2.8: Example of Instruction Operation                        | 27  |

| Figure 2.9: Example of Instruction Exception                        |     |

| Figure 2.10: Example of Instruction Programming Notes               |     |

| Figure 2.11: COP_LW Pseudocode Function                             |     |

| Figure 2.12: COP_LD Pseudocode Function                             |     |

| Figure 2.13: COP_SW Pseudocode Function                             |     |

| Figure 2.14: COP_SD Pseudocode Function                             |     |

| Figure 2.15: CoprocessorOperation Pseudocode Function               |     |

| Figure 2.16: MisalignedSupport Pseudocode Function                  |     |

| Figure 2.17: AddressTranslation Pseudocode Function                 |     |

| Figure 2.18: LoadMemory Pseudocode Function                         |     |

| Figure 2.19: StoreMemory Pseudocode Function                        |     |

| Figure 2.20: Prefetch Pseudocode Function                           |     |

| Figure 2.21: SyncOperation Pseudocode Function                      |     |

| Figure 2.22: ValueFPR Pseudocode Function                           |     |

| Figure 2.23: StoreFPR Pseudocode Function                           |     |

| Figure 2.24: CheckFPException Pseudocode Function                   |     |

| Figure 2.25: FPConditionCode Pseudocode Function                    |     |

| Figure 2.26: SetFPConditionCode Pseudocode Function                 |     |

| Figure 2.27: sign_extend Pseudocode Functions                       |     |

| Figure 2.28: memory_address Pseudocode Function                     |     |

| Figure 2.29: Instruction Fetch Implicit memory_address Wrapping     |     |

| Figure 2.30: AddressTranslation implicit memory_address Wrapping    | 38  |

| Figure 2.31: SignalException Pseudocode Function                    |     |

| Figure 2.32: SignalDebugBreakpointException Pseudocode Function     |     |

| Figure 2.33: SignalDebugModeBreakpointException Pseudocode Function |     |

| Figure 2.34: NullifyCurrentInstruction PseudoCode Function          |     |

| Figure 2.35: NotWordValue Pseudocode Function                       |     |

| Figure 2.36: PolyMult Pseudocode Function                           |     |

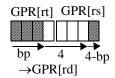

| Figure 3.1: ALIGN operation (32-bit)                                |     |

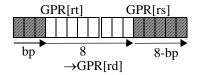

| Figure 3.2: DALIGN operation (64-bit)                               |     |

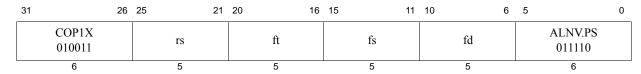

| Figure 3.3: Example of an ALNV.PS Operation                         | 54  |

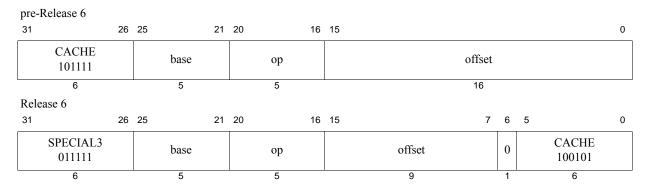

| Figure 3.4: Usage of Address Fields to Select Index and Way         |     |

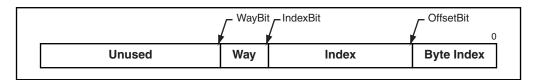

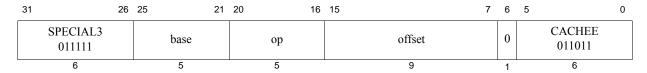

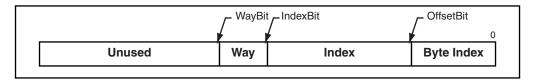

| Figure 3.5: Usage of Address Fields to Select Index and Way         |     |

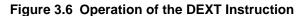

| Figure 3.6: Operation of the DEXT Instruction                       |     |

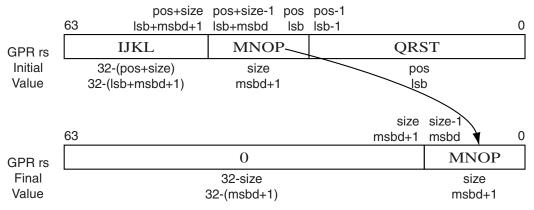

| Figure 3.7: Operation of the DEXTM Instruction                      |     |

| Figure 3.8: Operation of the DEXTU Instruction                      |     |

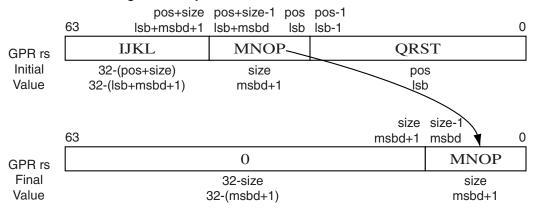

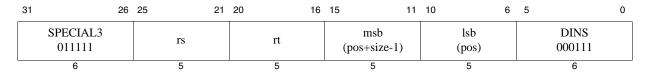

| Figure 3.9: Operation of the DINS Instruction.                      |     |

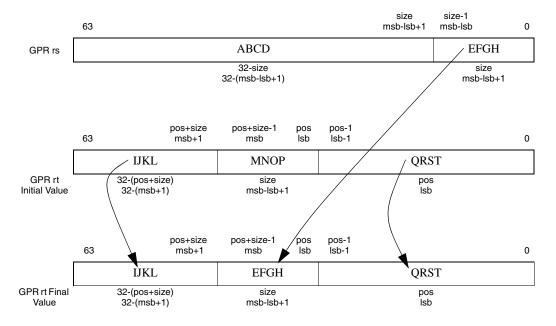

| Figure 3.10: Operation of the DINSM Instruction                     |     |

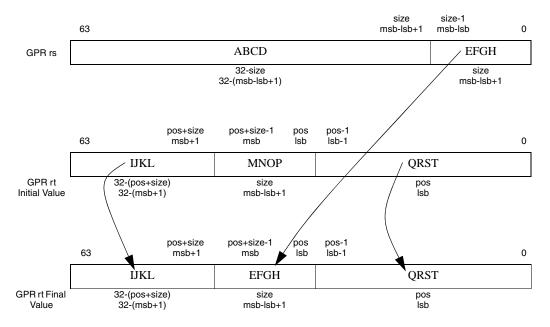

| Figure 3.11: Operation of the DINSU Instruction                     | 193 |

| Figure 3.12: Operation of the EXT Instruction            | 237 |

|----------------------------------------------------------|-----|

| Figure 3.13: Operation of the INS Instruction            | 246 |

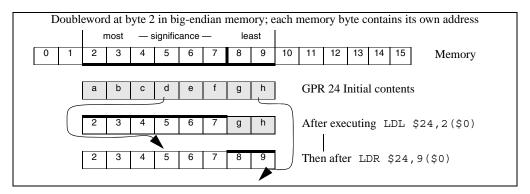

| Figure 3.14: Unaligned Doubleword Load Using LDL and LDR | 273 |

| Figure 3.15: Bytes Loaded by LDL Instruction             |     |

| Figure 3.16: Unaligned Doubleword Load Using LDR and LDL | 276 |

| Figure 3.17: Bytes Loaded by LDR Instruction             |     |

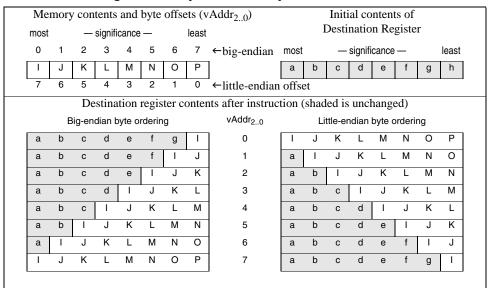

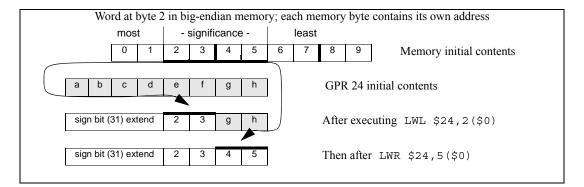

| Figure 5.1: Unaligned Word Load Using LWL and LWR        | 303 |

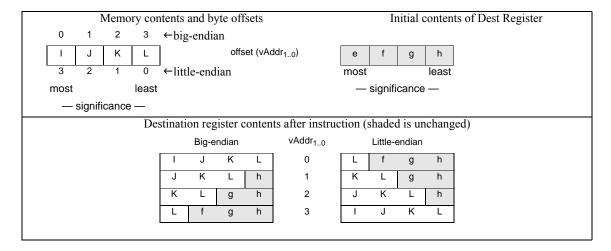

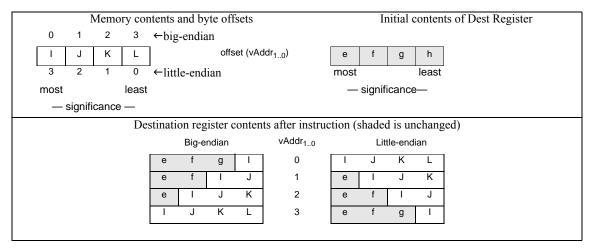

| Figure 5.2: Bytes Loaded by LWL Instruction              | 304 |

| Figure 5.3: Bytes Loaded by LWL Instruction              | 304 |

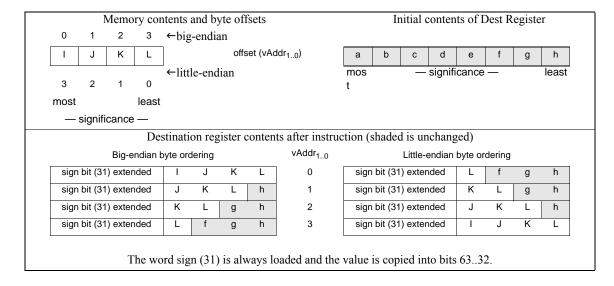

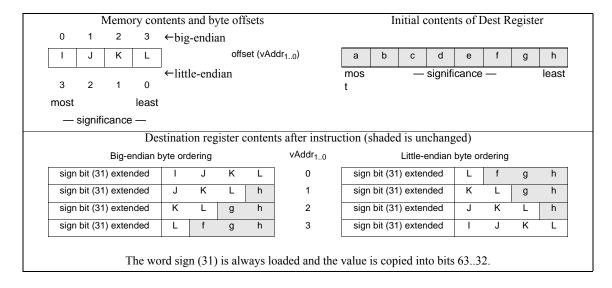

| Figure 5.4: Unaligned Word Load Using LWLE and LWRE      | 307 |

| Figure 5.5: Bytes Loaded by LWLE Instruction             | 308 |

| Figure 5.6: Bytes Loaded by LWLE Instruction             | 308 |

| Figure 5.7: Unaligned Word Load Using LWL and LWR        | 311 |

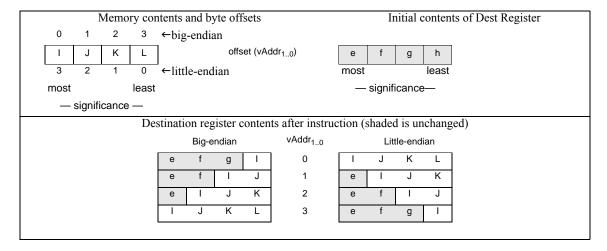

| Figure 5.8: Bytes Loaded by LWR Instruction              | 312 |

| Figure 5.9: Bytes Loaded by LWR Instruction              | 312 |

| Figure 5.10: Unaligned Word Load Using LWLE and LWRE     | 315 |

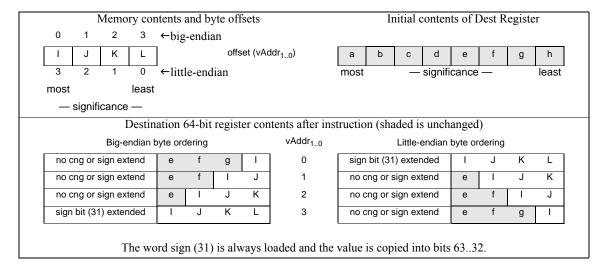

| Figure 5.11: Bytes Loaded by LWRE Instruction            | 315 |

| Figure 5.12: Bytes Loaded by LWRE Instruction            | 316 |

| Figure 6.13: Unaligned Doubleword Store With SDL and SDR | 439 |

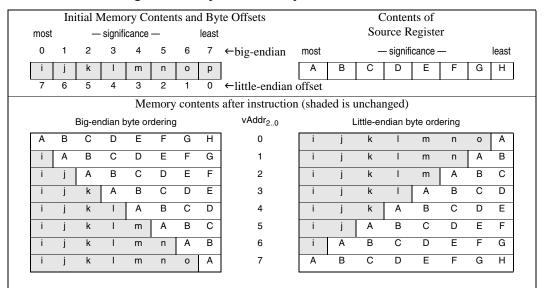

| Figure 6.14: Bytes Stored by an SDL Instruction          |     |

| Figure 6.15: Unaligned Doubleword Store With SDR and SDL | 441 |

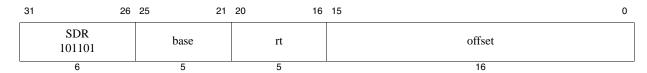

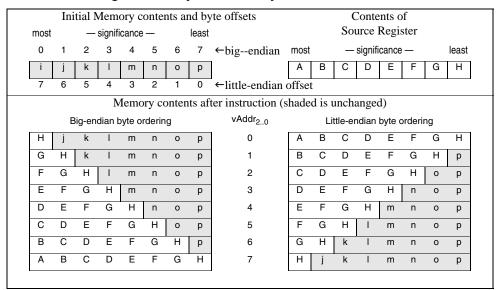

| Figure 6.16: Bytes Stored by an SDR Instruction          |     |

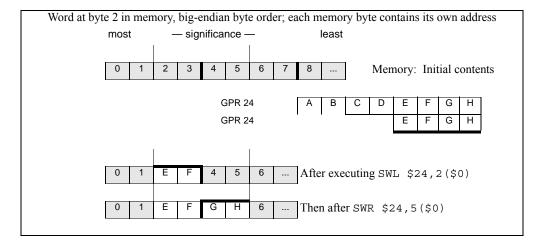

| Figure 6.17: Unaligned Word Store Using SWL and SWR      | 478 |

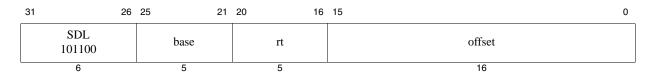

| Figure 6.18: Bytes Stored by an SWL Instruction          |     |

| Figure 6.19: Unaligned Word Store Using SWLE and SWRE    | 481 |

| Figure 6.20: Bytes Stored by an SWLE Instruction         |     |

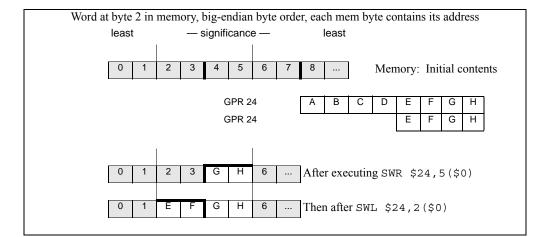

| Figure 6.21: Unaligned Word Store Using SWR and SWL      | 483 |

| Figure 6.22: Bytes Stored by SWR Instruction             | 484 |

| Figure 6.23: Unaligned Word Store Using SWRE and SWLE    | 486 |

| Figure 6.24: Bytes Stored by SWRE Instruction            |     |

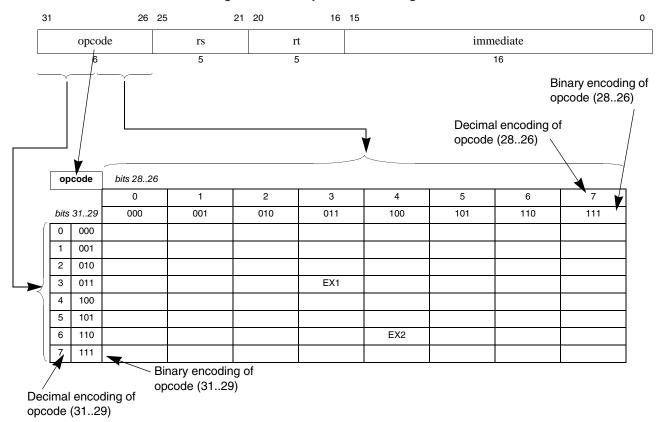

| Figure A.1: Sample Bit Encoding Table                    | 532 |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                             | 16  |

|-----------------------------------------------------------------------------------------|-----|

| Table 1.2: Read/Write Register Field Notation                                           | 19  |

| Table 2.1: AccessLength Specifications for Loads/Stores                                 |     |

| Table 3.1: FPU Comparisons Without Special Operand Exceptions                           | 123 |

| Table 3.2: FPU Comparisons With Special Operand Exceptions for QNaNs                    | 124 |

| Table 3.3: Usage of Effective Address                                                   | 126 |

| Table 3.4: Encoding of Bits[17:16] of CACHE Instruction                                 | 127 |

| Table 3.5: Encoding of Bits [20:18] of the CACHE Instruction                            | 128 |

| Table 3.6: Usage of Effective Address                                                   | 133 |

| Table 3.7: Encoding of Bits[17:16] of CACHEE Instruction                                | 134 |

| Table 3.8: Encoding of Bits [20:18] of the CACHEE Instruction                           | 135 |

| Table 3.1: Types of Global TLB Invalidates                                              |     |

| Table 5.1: Special Cases for FP MAX, MIN, MAXA, MINA                                    | 329 |

| Table 6.2: Values of hint Field for PREF Instruction                                    |     |

| Table 6.3: Values of hint Field for PREFE Instruction                                   | 394 |

| Table 6.4: RDHWR Register Numbers                                                       | 400 |

| Table 6.5: Encodings of the Bits[10:6] of the SYNC instruction; the SType Field         | 491 |

| Table A.1: Symbols Used in the Instruction Encoding Tables                              | 532 |

| Table A.2: MIPS64 Encoding of the Opcode Field                                          | 534 |

| Table A.3: MIPS64 SPECIAL Opcode Encoding of Function Field                             | 535 |

| Table A.4: MIPS64 REGIMM Encoding of rt Field                                           | 535 |

| Table A.5: MIPS64 SPECIAL2 Encoding of Function Field                                   | 536 |

| Table A.6: MIPS64 SPECIAL3 Encoding of Function Field for Release 2 of the Architecture | 536 |

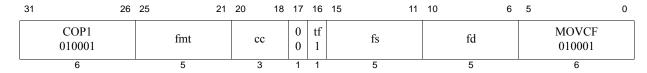

| Table A.7: MIPS64 MOVCI6R Encoding of tf Bit                                            | 536 |

| Table A.8: MIPS64 SRL Encoding of Shift/Rotate                                          | 537 |

| Table A.9: MIPS64 SRLV Encoding of Shift/Rotate                                         | 537 |

| Table A.10: MIPS64 DSRLV Encoding of Shift/Rotate                                       | 537 |

| Table A.11: MIPS64 DSRL Encoding of Shift/Rotate                                        |     |

| Table A.12: MIPS64 DSRL32 Encoding of Shift/Rotate                                      | 538 |

| Table A.13: MIPS64 BSHFL and DBSHFL Encoding of sa Field                                |     |

| Table A.14: MIPS64 COP0 Encoding of rs Field                                            |     |

| Table A.15: MIPS64 COP0 Encoding of Function Field When rs=CO                           |     |

| Table A.16: PCREL Encoding of Minor Opcode Field                                        | 539 |

| Table A.17: MIPS64 Encoding of rs Field                                                 |     |

| Table A.18: MIPS64 COP1 Encoding of Function Field When rs=S                            |     |

| Table A.19: MIPS64 COP1 Encoding of Function Field When rs=D                            |     |

| Table A.20: MIPS64 COP1 Encoding of Function Field When rs=W or L                       |     |

| Table A.21: MIPS64 COP1 Encoding of Function Field When rs=PS                           | 541 |

| Table A.22: MIPS64 COP1 Encoding of tf Bit When rs=S, D, or PS6R, Function=MOVCF6R      | 542 |

| Table A.23: MIPS64 COP2 Encoding of rs Field                                            |     |

| Table A.24: MIPS64 COP1X6R Encoding of Function Field                                   |     |

| Table A.25: Floating Point Unit Instruction Format Encodings                            |     |

| Table A.26: Release 6 MUL/DIV encodings                                                 |     |

| Table A.27: Release 6 PC-relative family encoding                                       |     |

| Table A.28: Release 6 PC-relative family encoding bitstrings                            |     |

| Table A.29: B*C compact branch encodings                                                | 547 |

# **About This Book**

The MIPS64® Instruction Set Reference Manual comes as part of a multi-volume set.

- Volume I-A describes conventions used throughout the document set, and provides an introduction to the MIPS64® Architecture

- Volume I-B describes conventions used throughout the document set, and provides an introduction to the micro-MIPS<sup>TM</sup> Architecture

- Volume II-A provides detailed descriptions of each instruction in the MIPS64® instruction set

- Volume II-B provides detailed descriptions of each instruction in the microMIPS64<sup>TM</sup> instruction set

- Volume III describes the MIPS64® and microMIPS64<sup>TM</sup> Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS® processor implementation

- Volume IV-a describes the MIPS16e<sup>™</sup> Application-Specific Extension to the MIPS64® Architecture. Beginning with Release 3 of the Architecture, microMIPS is the preferred solution for smaller code size. Release 6 removes MIPS16e: MIPS16e cannot be implemented with Release 6.

- Volume IV-b describes the MDMX<sup>™</sup> Application-Specific Extension to the MIPS64® Architecture and microMIPS64<sup>™</sup>. It is not applicable to the MIPS32® document set nor the microMIPS32<sup>™</sup> document set. With Release 5 of the Architecture, MDMX is deprecated. MDMX and MSA can not be implemented at the same time. Release 6 removes MDMX: MDMX cannot be implemented with Release 6.

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS® Architecture. Release 6 removes MIPS-3D: MIPS-3D cannot be implemented with Release 6.

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and the microMIPS32™ Architecture and is not applicable to the MIPS64® document set nor the microMIPS64™ document set. Release 6 removes SmartMIPS: SmartMIPS cannot be implemented with Release 6, neither MIPS32 Release 6 nor MIPS64 Release 6.

- Volume IV-e describes the MIPS® DSP Module to the MIPS® Architecture.

- Volume IV-f describes the MIPS® MT Module to the MIPS® Architecture

- Volume IV-h describes the MIPS® MCU Application-Specific Extension to the MIPS® Architecture

- Volume IV-i describes the MIPS® Virtualization Module to the MIPS® Architecture

- Volume IV-j describes the MIPS® SIMD Architecture Module to the MIPS® Architecture

## 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, and *registers* that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S* and *D*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through 1

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

#### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

• Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in another process

- **UNPREDICTABLE** operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described using a high-level language pseudocode resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

Symbol Meaning  $\leftarrow$ Assignment =,  $\neq$ Tests for equality and inequality Bit string concatenation A y-bit string formed by y copies of the single-bit value x $\mathbf{x}^{y}$ b#n A constant value n in base b. For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. A constant value n in base 2. For instance 0b100 represents the binary value 100 (decimal 4). 0bn A constant value n in base 16. For instance 0x100 represents the hexadecimal value 100 (decimal 256). 0xn

**Table 1.1 Symbols Used in Instruction Operation Statements**

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                                        | Meaning                                                                                                                                                                                                                                                       |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x <sub>yz</sub>                               | Selection of bits $y$ through $z$ of bit string $x$ . Little-endian bit notation (rightmost bit is 0) is used. If $y$ is less than $z$ , this expression is an empty (zero length) bit string.                                                                |

| x.bit[y]                                      | Bit y of bitstring x. Alternative to the traditional MIPS notation $x_y$ .                                                                                                                                                                                    |

| x.bits[yz]                                    | Selection of bits y through z of bit string x. Alternative to the traditional MIPS notation $x_{yz}$ .                                                                                                                                                        |

| x.byte[y]                                     | Byte y of bitstring x. Equivalent to the traditional MIPS notation $x_{8*y+78*y}$ .                                                                                                                                                                           |

| x.bytes[yz]                                   | Selection of bytes y through z of bit string x. Alternative to the traditional MIPS notation $x_{8*y+78*z}$ .                                                                                                                                                 |

| x.halfword[y]<br>x.word[i]<br>x.doubleword[i] | Similar extraction of particular bitfields (used in e.g., MSA packed SIMD vectors).                                                                                                                                                                           |

| x.bit31, x.byte0, etc.                        | Examples of abbreviated form of x.bit[y], etc. notation, when y is a constant.                                                                                                                                                                                |

| x.fieldy                                      | Selection of a named subfield of bitstring <i>x</i> , typically a register or instruction encoding.  More formally described as "Field y of register x".  For example, FIR.D = "the D bit of the Coprocessor 1 Floating-point Implementation Register (FIR)". |

| +, -                                          | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                            |

| *,×                                           | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                        |

| div                                           | 2's complement integer division                                                                                                                                                                                                                               |

| mod                                           | 2's complement modulo                                                                                                                                                                                                                                         |

| /                                             | Floating point division                                                                                                                                                                                                                                       |

| <                                             | 2's complement less-than comparison                                                                                                                                                                                                                           |

| >                                             | 2's complement greater-than comparison                                                                                                                                                                                                                        |

| <b>≤</b>                                      | 2's complement less-than or equal comparison                                                                                                                                                                                                                  |

| ≥                                             | 2's complement greater-than or equal comparison                                                                                                                                                                                                               |

| nor                                           | Bitwise logical NOR                                                                                                                                                                                                                                           |

| xor                                           | Bitwise logical XOR                                                                                                                                                                                                                                           |

| and                                           | Bitwise logical AND                                                                                                                                                                                                                                           |

| or                                            | Bitwise logical OR                                                                                                                                                                                                                                            |

| not                                           | Bitwise inversion                                                                                                                                                                                                                                             |

| &&                                            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                     |

| <<                                            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                        |

| >>                                            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                        |

| GPRLEN                                        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                            |

| GPR[x]                                        | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                  |

| SGPR[s,x]                                     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose registers may be implemented. SGPR[s,x] refers to GPR set s, register x.                                                                                 |

| FPR[x]                                        | Floating Point operand register x                                                                                                                                                                                                                             |

| FCC[CC]                                       | Floating Point condition code CC. FCC[0] has the same value as COC[1]. Release 6 removes the floating point condition codes.                                                                                                                                  |

| FPR[x]                                        | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPR[z,x,s]           | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CP2CPR[x]            | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CCR[z,x]             | Coprocessor unit z, control register x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CP2CCR[x]            | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| COC[z]               | Coprocessor unit z condition signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Xlat[x]              | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BigEndianMem         | Endian mode as configured at chip reset ( $0 \rightarrow \text{Little-Endian}$ , $1 \rightarrow \text{Big-Endian}$ ). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions) and the endianness of Kernel and Supervisor mode execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BigEndianCPU         | The endianness for load and store instructions ( $0 \rightarrow \text{Little-Endian}$ , $1 \rightarrow \text{Big-Endian}$ ). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ReverseEndian        | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as (SR <sub>RE</sub> and User mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> .  The effect of pseudocode statements for the current instruction labeled <b>I+1</b> appears to occur "at the same time" as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |

| PC                   | The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time by any pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16e instruction) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during the instruction time of the instruction in the branch delay slot.  In the MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the restart address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception. Release 6 adds PC-relative address computation and load instructions. The PC value contains a full 64-bit address, all of which are significant during a memory reference.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                                                               |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------|--|--|--|

| ISA Mode                             | In processors that implement the MIPS16e Application Specific Extension or the microMIPS base architectures, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing, as follows:                                                                                                                                                                                                                            |  |                                                               |  |  |  |

|                                      | Encoding Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |                                                               |  |  |  |

|                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | The processor is executing 32-bit MIPS instructions           |  |  |  |

|                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | The processor is executing MIIPS16e or microMIPS instructions |  |  |  |

|                                      | In the MIPS Architecture, the <i>ISA Mode</i> value is only visible indirectly, such as when the processor stores a combined value of the upper bits of PC and the <i>ISA Mode</i> into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception.                                                                                                                                                         |  |                                                               |  |  |  |

| PABITS                               | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{PABITS} = 2^{36}$ bytes.                                                                                                                                                                                                                                   |  |                                                               |  |  |  |

| SEGBITS                              | The number of virtual address bits implemented in a segment of the address space is represented by the symbol SEGBITS. As such, if 40 virtual address bits are implemented in a segment, the size of the segment is $2^{\text{SEGBITS}} = 2^{40}$ bytes.                                                                                                                                                                                                   |  |                                                               |  |  |  |

| FP32RegistersMode                    | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). In MIPS32 Release 1, the FPU has 32, 32-bit FPRs, in which 64-bit data types are stored in even-odd pairs of FPRs. In MIPS64, (and optionally in MIPS32 Release 2 and Release 3) the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                              |  |                                                               |  |  |  |

|                                      | In MIPS32 Release 1 implementations, <b>FP32RegistersMode</b> is always a 0. MIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32, 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs. |  |                                                               |  |  |  |

|                                      | The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register.                                                                                                                                                                                                                                                                                                                                                           |  |                                                               |  |  |  |

| InstructionInBranchDe-<br>laySlot    | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                            |  |                                                               |  |  |  |

| SignalException(exception, argument) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function—the exception is signaled at the point of the call.                                                                                                                                                                                        |  |                                                               |  |  |  |

# 1.4 Notation for Register Field Accessibility

In this document, the read/write properties of register fields use the notations shown in Table 1.1.

Table 1.2 Read/Write Register Field Notation

| Read/Write<br>Notation | Hardware Interpretation                                                                                                      | Software Interpretation                                                                                                                                                                                                |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/W                    | Hardware updates of this field are visible by softwar hardware read. If the Reset State of this field is "Undefined", either | f the Reset State of this field is "Undefined", either software or hardware must initialize the value before the first read will return a predictable value. This should not be confused with the formal definition of |  |  |  |

Table 1.2 Read/Write Register Field Notation (Continued)